|

|

PDF FTF3020-C Data sheet ( Hoja de datos )

| Número de pieza | FTF3020-C | |

| Descripción | Full Frame CCD Image Sensor | |

| Fabricantes | NXP Semiconductors | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de FTF3020-C (archivo pdf) en la parte inferior de esta página. Total 16 Páginas | ||

|

No Preview Available !

IMAGE SENSORS

FTF3020-C

Full Frame CCD Image Sensor

Product specification

File under Image Sensors

1999 November 22

Philips

Semiconductors

1 page

Philips Semiconductors

Full Frame CCD Image Sensor

Product specification

FTF3020-C

Specifications

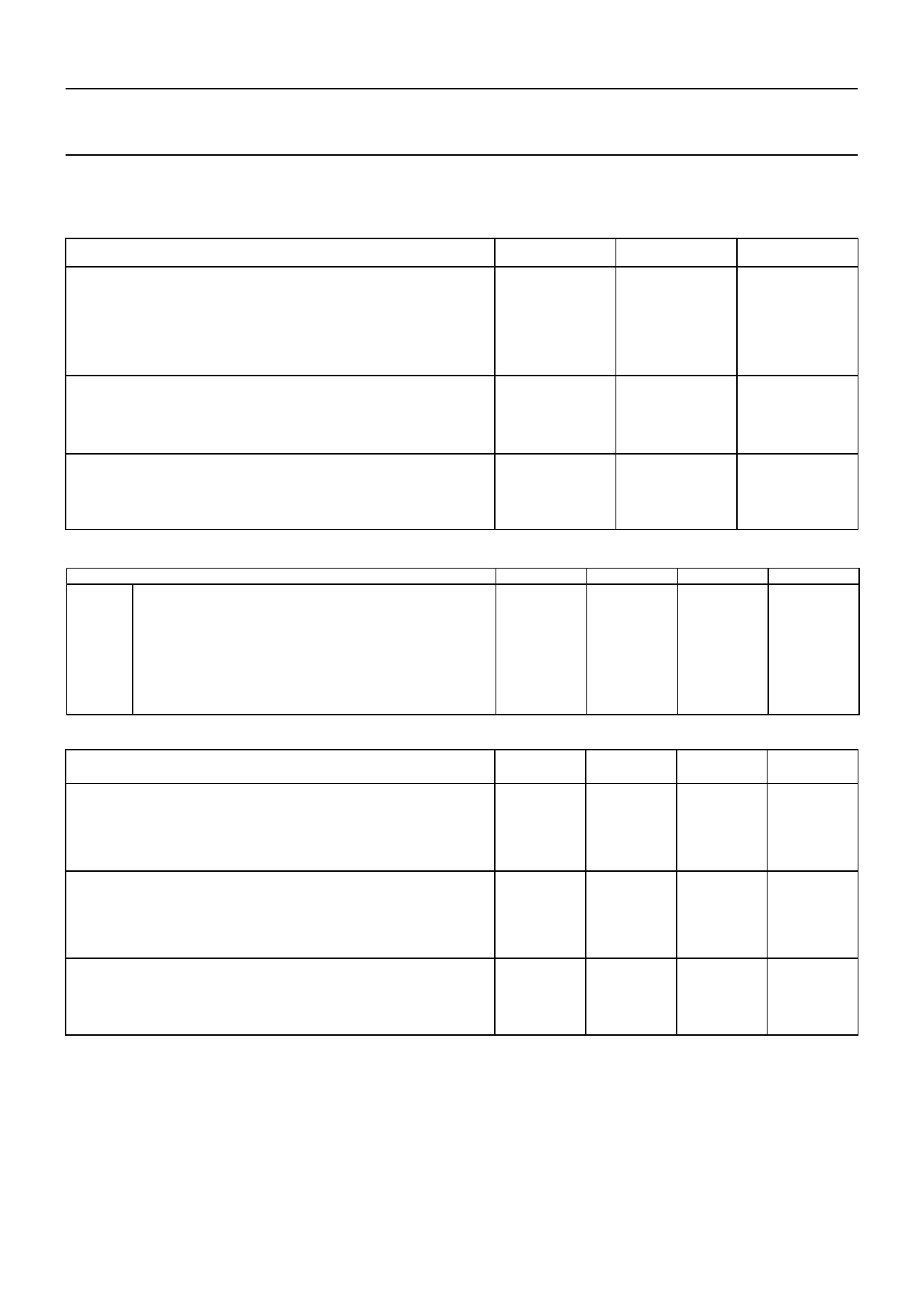

ABSOLUTE MAXIMUM RATINGS1

GENERAL:

storage temperature

ambient temperature during operation

voltage between any two gates

DC current through any clock phase (absolute value)

OUT current (no short circuit protection)

VOLTAGES IN RELATION TO VPS:

VNS, SFD, RD

VCS, SFS

all other pins

VOLTAGES IN RELATION TO VNS:

SFD, RD

VCS, SFS, VPS

all other pins

VNS3

VPS

SFD

SFS

VCS

OG

RD

DC CONDITIONS2

N substrate

P substrate

Source Follower Drain

Source Follower Source

Current Source

Output Gate

Reset Drain

MIN.

-55

-40

-20

-0.2

0

-0.5

-8

-5

-15

-30

-30

MAX.

+80

+60

+20

+2.0

10

+30

+5

+25

+0.5

+0.5

+0.5

UNIT

°C

°C

V

µA

mA

V

V

V

V

V

V

MIN. [V]

18

1

16

0

-5

4

13

TYPICAL [V] MAX. [V]

24

3

20

0

0

6.5

15.5

28

7

24

0

3

8

18

MAX. [mA]

15

15

4.5

1

-

-

-

AC CLOCK LEVEL CONDITIONS2

IMAGE CLOCKS:

A-clock amplitude during integration and hold

A-clock amplitude during vertical transport (duty cycle=5/8) 4

A-clock low level

Charge Reset (CR) level on A-clock 5

OUTPUT REGISTER CLOCKS:

C-clock amplitude (duty cycle during hor. transport = 3/6)

C-clock low level

Summing Gate (SG) amplitude

Summing Gate (SG) low level

OTHER CLOCKS:

Reset Gate (RG) amplitude

Reset Gate (RG) low level

Charge Reset (CR) pulse on Nsub 5

MIN.

8

10

-5

4.75

2

5

0

TYPICAL

MAX.

UNIT

10 V

14 V

0V

-5 V

5 5.25 V

3.5 V

10 10 V

3.5 V

10 10 V

3V

10 10 V

1 During Charge Reset it is allowed to exceed maximum rating levels (see note 5).

2 All voltages in relation to SFS.

3 To set the VNS voltage for optimal Vertical Anti-Blooming (VAB), it should be adjustable between minimum and maximum values.

4 Three-level clock is preferred for maximum charge; the swing during vertical transport should be 4V higher than the voltage during integration.

A two level clock (typically 10V) can be used if a lower maximum charge handling capacity is allowed.

5 Charge Reset can be achieved in two ways:

• The typical A-clock low level is applied to all image clocks; for proper CR, an additional Charge Reset pulse on VNS is required (preferred).

• The typical CR level is applied to all image clocks simultaneously.

1999 November

5

5 Page

Philips Semiconductors

Full Frame CCD Image Sensor

Product specification

FTF3020-C

OUTPUT BUFFERS

MIN.

TYPICAL

MAX.

Conversion factor

Mutual conversion factor matching (∆ACF)1

Supply current

Bandwidth

Output impedance buffer (Rload = 3.3kΩ, Cload = 2pF)

5 7.5 10

02

4.5

110

400

1 Matching of the four outputs is specified as ∆ACF with respect to reference measured at the operating point (Qlin/2).

UNIT

µV/el.

µV/el.

mA

MHz

Ω

DARK CONDITION

Dark current level @ 30° C

Dark current level @ 60° C

Fixed Pattern Noise 1 (FPN) @ 60° C

RMS readout noise @ 9MHz bandwidth after CDS

1 FPN is the one-σ value of the highpass image.

MIN.

TYPICAL

MAX.

20 30

0.3 0.6

15 25

25 30

UNIT

pA/cm2

nA/cm2

el.

el.

Dark Current

1000

100

10

1

0 10 20 30 40 50 60

Temp. (oC)

1999 November

Figure 10 - Dark current versus temperature

11

11 Page | ||

| Páginas | Total 16 Páginas | |

| PDF Descargar | [ Datasheet FTF3020-C.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| FTF3020-C | Full Frame CCD Image Sensor | NXP Semiconductors |

| FTF3020-M | Full Frame CCD Image Sensor | NXP Semiconductors |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |