|

|

PDF 8T49N488 Data sheet ( Hoja de datos )

| Número de pieza | 8T49N488 | |

| Descripción | NG QUAD Universal Frequency Translator | |

| Fabricantes | Integrated Device Technology | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de 8T49N488 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

FemtoClock® NG QUAD Universal

Frequency Translator

8T49N488

DATA SHEET

General Description

The 8T49N488 is a quad PLL with FemtoClock® NG technology, it

integrates low phase noise Frequency Translator / Synthesizer, Jitter

attenuation, and with alarm and monitoring functions suitable for

networking and communications applications. The device has four

fully independent PLLs, each PLL is able to generate any output

frequency in the 0.98MHz - 312.5MHz range and most output

frequencies in the 312.5MHz - 1,300MHz range (see Table 3 for

details). A wide range of input reference clocks and operation

reference clock may be used as the source for the output frequency.

Each PLL of 8T49N488 has three operating modes to support a very

broad spectrum of applications:

1) Frequency Synthesizer

• Synthesizes output frequencies from an external reference

clock REFCLK.

• Fractional feedback division is used, so there are no

requirements for any specific input reference clock frequency to

produce the desired output frequency with a high degree of

accuracy.

2) High-Bandwidth Frequency Translator

• Applications: PCI Express, Computing, General Purpose

• Translates any input clock in the 16MHz - 710MHz frequency

range into any supported output frequency.

• This mode has a high PLL loop bandwidth in order to track input

reference changes, such as Spread-Spectrum Clock

modulation.

3) Low-Bandwidth Frequency Translator

• Applications: Networking & Communications.

• Translates any input clock in the 8kHz -710MHz frequency

range into any supported output frequency.

• This mode supports PLL loop bandwidths in the 10Hz - 580Hz

range and makes use of an external REFCLK to provide

significant jitter attenuation.

Each PLL provides factory-programmed default power-up

configuration burned into One-Time Programmable (OTP) memory.

The configuration is specified by customer and are programmed by

IDT during the final test phase from an on-hand stock of blank

devices.

To implement other configurations, these power-up default settings

can be overwritten after power-up using the I2C interface and the

device can be completely reconfigured.

Features

• Fourth generation FemtoClock® NG technology

• Four fully independent PLLs

• Universal Frequency TranslatorTM/Frequency Synthesizer and

Jitter attenuator

• Outputs are programmable as LVPECL or LVDS

• Programmable output frequency: 0.98MHz up to 1,300MHz

• Two differential inputs support the following input levels:

LVPECL, LVDS, LVHSTL, HCSL

• Input frequency range: 8kHz ~ 710MHz Low-Bandwidth

• Input frequency range: 16MHz ~ 710MHz High-Bandwidth

• REFCLK frequency range: 16MHz ~ 40MHz

• Input clock monitor and alarm

• Smoothed reference switch

• Factory-set register configuration for power-up default state

• Power-up default configuration

• Configuration customized via One-Time Programmable ROM

• Settings may be overwritten after power-up via I2C

• I2C Serial interface for register programming

• RMS phase jitter at 161.1328125MHz,using 40MHz REFCLK

(12kHz ~ 20MHz): 465fs (typical), Low Bandwidth Mode (FracN)

• RMS phase jitter at 400MHz,using 40MHz REFCLK

(12kHz ~ 20MHz): 333fs (typical), Synthesizer Mode (Integer FB)

• Full 2.5V ±5% supply mode

• -40°C to 85°C ambient operating temperature

• 10mm X 10mm CABGA package

• Lead-free (RoHS 6) packaging

8T49N488 REVISION B 03/23/15

1 ©2015 Integrated Device Technology, Inc.

1 page

Table 2. Pin Characteristics

Symbol

Parameter

CIN

RPULLUP

RPULLDOWN

RPULLDOWN

Input Capacitance

Input Pullup Resistor

Input Pulldown Resistor

Input Pulldown REFCLK,

Resistor

PLL_BYPASS

RPULLUP

Input Pullup

Resistor

SDATA, SCLK

Pin Assignment

8T49N488 DATA SHEET

Test Conditions

Minimum

Typical

3.5

51

51

12.5

Maximum

Units

pF

k

k

k

12.5 k

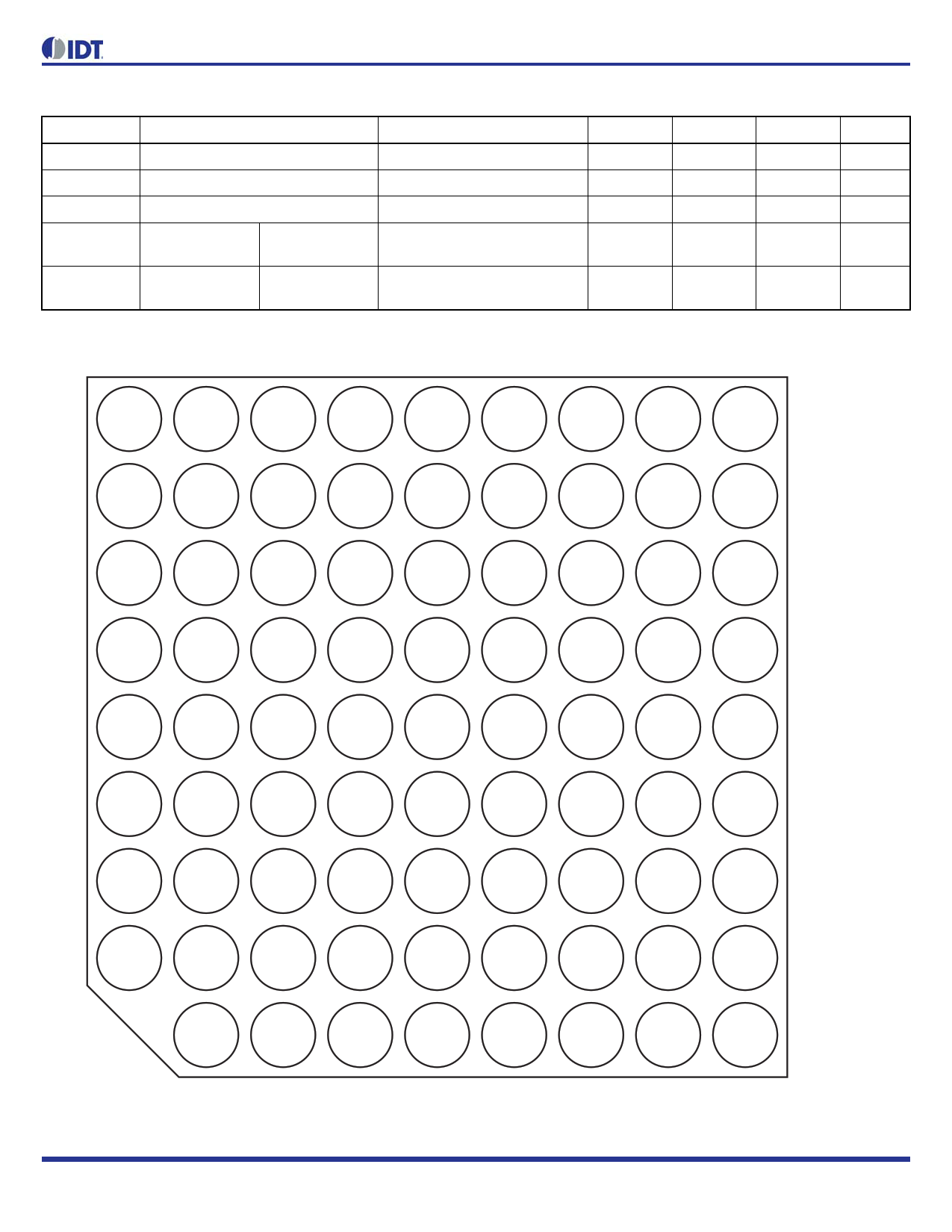

J

Q0D

VEE_D VCCO_D

nQ1C

LF1C

LF0C

VEE_C

nQ0C

Q0C

H nQ0D

VEE_D

CLK0D nCLK0D LOCKD

Q1C

RSVD

VEE_C

VEE_C

G VEE_D

RSVD

CLK1D nCLK1D

SCLK

SDATA

CLK1C

CLK0C VCCO_C

F LF0D

Q1D

VCC_D CLK_SELD VCC_C CLK_SELC nCLK1C nCLK0C

nQ1B

E

LF1D

LOCKA VCCA_D

RSVD

REFCLK

PLL_BY

PASS

VCCA_C

LOCKC

LF1B

D nQ1D nCLK0A nCLK1A CLK_SELA VCCO_B CLK_SELB VCC_B

Q1B

LF0B

C VCCA_A CLK0A

CLK1A VCCO_A LOCKB NCLK1B CLK1B

RSVD

VEE_B

B Q0A

VEE_A

VEE_A

Q1A

VCC_A nCLK0B CLK0B

VEE_B

nQ0B

A

nQ0A

VEE_A

LF0A

LF1A

nQ1A

VCCA_B VEE_B

Q0B

1 2 3 45 6 7 8 9

8T49N488 Pin Map (bottom view)

REVISION B 03/23/15

5 FEMTOCLOCK®NG QUAD UNIVERSAL FREQUENCY TRANSLATOR

5 Page

8T49N488 DATA SHEET

Table 4E. Configuration-Specific Control Bits

Register Bits

Function

Q0_TYPEx

Determines the output type for output pair Q0, nQ0 for PLLx.

0 = LVPECL

1 = LVDS

Q1_TYPEx

Determines the output type for output pair Q1, nQ1 for PLLx.

0 = LVPECL

1 = LVDS

Px[16:0]

Reference Pre-Divider for PLLx.

M1_x[16:0]

Integer Feedback Divider in Lower Feedback Loop for PLLx.

M_INTx[7:0]

Feedback Divider, Integer Value in Upper Feedback Loop for PLLx.

M_FRACx[17:0] Feedback Divider, Fractional Value in Upper Feedback Loop for PLLx.

Nx[10:0]

Output Divider for PLLx.

BWx[6:0]

Internal Operation Settings for PLLx.

Please use IDT 8T49N488 Configuration Software to determine the correct settings for these bits for the specific

configuration. Alternatively, please consult with IDT directly for further information on the functions of these bits.The

function of these bits are explained in Tables 4H and 4I.

Table 4F. Global Control Bits

Register Bits

Function

MODE_SELx[1:0]

PLL Mode Select for PLLx.

00 = Low Bandwidth Frequency Translator

01 = Frequency Synthesizer

10 = High Bandwidth Frequency Translator

11 = High Bandwidth Frequency Translator

OE0_x

Output Enable Control for Output 0 for PLLx.

0 = Output Q0, nQ0 disabled

1 = Output Q0, nQ0 enabled

OE1_x

Output Enable Control for Output 1 for PLLx.

0 = Output Q1, nQ1 disabled

1 = Output Q1, nQ1 enabled

Rsvd

Reserved bits - user should write a ‘0’ to these bit positions if a write to these registers is needed

AUTO_MANx[1:0]

Selects how input clock selection is performed for PLLx.

00 = Manual Selection via pin only

01 = Automatic, non-revertive

10 = Automatic, revertive

11 = Manual Selection via register only

CLK_SELx

In manual clock selection via register mode for PLLx, this bit will command which input clock is selected. In the

automatic modes, this indicates the primary clock input. In manual selection via pin mode, this bit has no effect.

0 = CLK0

1 = CLK1

ADC_RATEx[1:0]

Sets the ADC sampling rate in Low-Bandwidth Mode as a fraction of the REFCLK input frequency for PLLx.

00 = REFCLK Frequency 16 when doubler is disabled

01 = REFCLK Frequency 8 when doubler is disabled

10 = REFCLK Frequency 4 (recommended) when doubler is disabled

11 = REFCLK Frequency 2 when doubler is disabled

LCK_WINx[1:0]

Sets the width of the window in which a new reference edge must fall relative to the feedback edge for PLLx.

00 = 2sec (recommended)

01 = 4sec

10 = 8sec

11 = 16sec

DBL_REFCLKx

When set, this bit will double the frequency of the REFCLK input before applying it to the Phase-Frequency

Detector for PLLx.

REVISION B 03/23/15

11 FEMTOCLOCK®NG QUAD UNIVERSAL FREQUENCY TRANSLATOR

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet 8T49N488.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| 8T49N4811 | I2C Programmable Ethernet Clock Generator | Integrated Device Technology |

| 8T49N488 | NG QUAD Universal Frequency Translator | Integrated Device Technology |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |