No Preview Available !

FEATURES

11-bit, 200 MSPS output data rate per channel

Integrated noise shaping requantizer (NSR)

Performance with NSR enabled

SNR: 75.5 dBFS in 40 MHz band to 70 MHz @ 185 MSPS

SNR: 73.7 dBFS in 60 MHz band to 70 MHz @ 185 MSPS

Performance with NSR disabled

SNR: 66.5 dBFS to 70 MHz @ 185 MSPS

SFDR: 83 dBc to 70 MHz @ 185 MSPS

Low power: 0.62 W @ 185 MSPS

1.8 V analog supply operation

1.8 V LVDS (ANSI-644 levels) output

1-to-8 integer clock divider

Internal ADC voltage reference

1.75 V p-p analog input range (programmable to 2.0 V p-p)

Differential analog inputs with 800 MHz bandwidth

95 dB channel isolation/crosstalk

Serial port control

User-configurable built-in self-test (BIST) capability

Energy-saving power-down modes

APPLICATIONS

Communications

Diversity radio and smart antenna (MIMO) systems

Multimode digital receivers (3G)

WCDMA, LTE, CDMA2000

WiMAX, TD-SCDMA

I/Q demodulation systems

www.DaGteanSehreaelt-4pUu.crpomose software radios

Dual IF Receiver

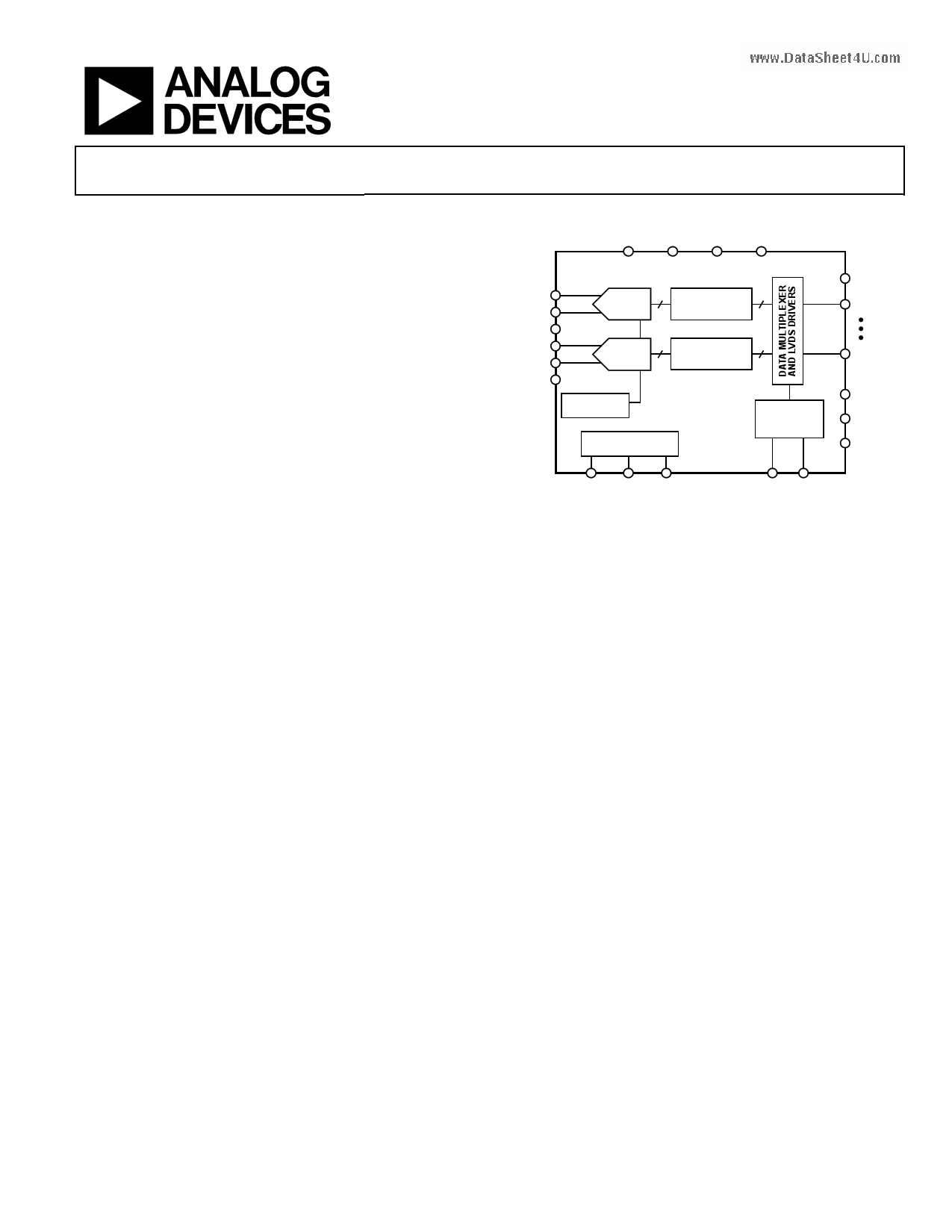

AD6642

FUNCTIONAL BLOCK DIAGRAM

AVDD AGND DRVDD DRGND

VIN+A

VIN–A

VCMA

VIN+B

VIN–B

VCMB

AD6642

PIPELINE 14 NOISE SHAPING 11

ADC

REQUANTIZER

PIPELINE 14 NOISE SHAPING 11

ADC

REQUANTIZER

REFERENCE

SERIAL PORT

CLOCK

DIVIDER

DC0±AB

D0±AB

D10±AB

MODE

SYNC

PDWN

SCLK SDIO CSB

Figure 1.

CLK+ CLK–

PRODUCT HIGHLIGHTS

1. Two ADCs are contained in a small, space-saving,

10 mm × 10 mm × 1.4 mm, 144-ball CSP_BGA package.

2. Pin selectable noise shaping requantizer (NSR) function

that allows for improved SNR within a reduced bandwidth

of up to 60 MHz at 185 MSPS.

3. LVDS digital output interface configured for low cost

FPGA families.

4. 120 mW per ADC core power consumption.

5. Operation from a single 1.8 V supply.

6. Standard serial port interface (SPI) that supports various

product features and functions, such as data formatting

(offset binary or twos complement), NSR, power-down,

test modes, and voltage reference mode.

7. On-chip integer 1-to-8 input clock divider and multichip

sync function to support a wide range of clocking schemes

and multichannel subsystems.

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarksandregisteredtrademarksarethepropertyoftheirrespectiveowners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

www.analog.com

Fax: 781.461.3113

©2009 Analog Devices, Inc. All rights reserved.

AD6642

AC SPECIFICATIONS

AVDD = 1.8 V, DRVDD = 1.8 V, fS = 185 MSPS, 1.75 V p-p differential input, VIN = −1.0 dBFS differential input, and default SPI, unless

otherwise noted.

Table 2.

Parameter1

SIGNAL-TO-NOISE-RATIO (SNR)—NSR DISABLED

fIN = 30 MHz

fIN = 70 MHz

fIN = 170 MHz

fIN = 250 MHz

SIGNAL-TO-NOISE-RATIO (SNR)—NSR ENABLED

22% BW Mode

fIN = 70 MHz

fIN = 170 MHz

fIN = 230 MHz

33% BW Mode

fIN = 70 MHz

fIN = 170 MHz

fIN = 230 MHz

SIGNAL-TO-NOISE-AND DISTORTION (SINAD)

fIN = 30 MHz

fIN = 70 MHz

fIN = 170 MHz

fIN = 250 MHz

EFFECTIVE NUMBER OF BITS (ENOB)

fIN = 30 MHz

fIN = 70 MHz

fIN = 170 MHz

fIN = 250 MHz

WORST SECOND OR THIRD HARMONIC

fIN = 30 MHz

www.DatafSINh=ee7t04UM.Hcozm

fIN = 170 MHz

fIN = 250 MHz

SPURIOUS-FREE DYNAMIC RANGE (SFDR)

fIN = 30 MHz

fIN = 70 MHz

fIN = 170 MHz

fIN = 250 MHz

WORST OTHER HARMONIC (FOURTH THROUGH EIGHTH)

fIN = 30 MHz

fIN = 70 MHz

fIN = 170 MHz

fIN = 250 MHz

TWO-TONE SFDR (−7 dBFS)

fIN1 = 169 MHz, fIN2 = 172 MHz

CROSSTALK2

ANALOG INPUT BANDWIDTH

Temperature Min

25°C

25°C

Full 65.7

25°C

25°C

Full 72.8

25°C

25°C

Full 71.0

25°C

25°C

25°C

Full 64.1

25°C

25°C

25°C

Full 10.3

25°C

25°C

25°C

Full −72

25°C

25°C

25°C

Full 72

25°C

25°C

25°C

Full −82

25°C

25°C

Full

25°C

Typ

66.5

66.5

66.1

65.5

75.5

74.4

72.8

73.7

72.6

71.0

65.5

66.3

65.6

64.3

10.6

10.7

10.6

10.3

−90

−83

−78

−80

90

83

78

80

−100

−96

−90

−95

82

95

800

Max

Unit

dBFS

dBFS

dBFS

dBFS

dBFS

dBFS

dBFS

dBFS

dBFS

dBFS

dBFS

dBFS

dBFS

dBFS

Bits

Bits

Bits

Bits

dBc

dBc

dBc

dBc

dBc

dBc

dBc

dBc

dBc

dBc

dBc

dBc

dBc

dB

MHz

1 See the AN-835 Application Note, Understanding High Speed ADC Testing and Evaluation, for a complete set of definitions.

2 Crosstalk is measured at 155 MHz with −1 dBFS on one channel and no input on the alternate channel.

Rev. 0 | Page 5 of 32

Pin No.

K8

J8

M8

L8

K9

J9

M9

L9

K10

J10

M10

L10

K11

J11

M11

L11

K12

J12

M12

L12

C9

C8

C7

C6

C5

C4

Mnemonic

D2+AB

D2−AB

D3+AB

D3−AB

D4+AB

D4−AB

D5+AB

D5−AB

D6+AB

D6−AB

D7+AB

D7−AB

D8+AB

D8−AB

D9+AB

D9−AB

D10+AB

D10−AB

DCO+AB

DCO−AB

MODE

SYNC

PDWN

SCLK

SDIO

CSB

AD6642

Type

Output

Output

Output

Output

Output

Output

Output

Output

Output

Output

Output

Output

Output

Output

Output

Output

Output

Output

Output

Output

Input

Input

Input

Input

Input/Output

Input

Description

Channel A and Channel B LVDS Output Data 2—True

Channel A and Channel B LVDS Output Data 2—Complement

Channel A and Channel B LVDS Output Data 3—True

Channel A and Channel B LVDS Output Data 3—Complement

Channel A and Channel B LVDS Output Data 4—True

Channel A and Channel B LVDS Output Data 4—Complement

Channel A and Channel B LVDS Output Data 5—True

Channel A and Channel B LVDS Output Data 5—Complement

Channel A and Channel B LVDS Output Data 6—True

Channel A and Channel B LVDS Output Data 6—Complement

Channel A and Channel B LVDS Output Data 7—True

Channel A and Channel B LVDS Output Data 7—Complement

Channel A and Channel B LVDS Output Data 8—True

Channel A and Channel B LVDS Output Data 8—Complement

Channel A and Channel B LVDS Output Data 9—True

Channel A and Channel B LVDS Output Data 9—Complement

Channel A and Channel B LVDS Output Data 10—True

Channel A and Channel B LVDS Output Data 10—Complement

Data Clock LVDS Output for Channel A and Channel B—True

Data Clock LVDS Output for Channel A and Channel B—Complement

Mode Select Pin (Logic Low Enables NSR; Logic High Disables NSR)

Digital Synchronization Pin

Power-Down Input (Active High)

SPI Clock

SPI Data

SPI Chip Select (Active Low)

www.DataSheet4U.com

Rev. 0 | Page 11 of 32