|

|

PDF U631H256 Data sheet ( Hoja de datos )

| Número de pieza | U631H256 | |

| Descripción | SoftStore 32K x 8 nvSRAM | |

| Fabricantes | Simtek | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de U631H256 (archivo pdf) en la parte inferior de esta página. Total 13 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

Not Recommended For New Designs

U631H256

SoftStore 32K x 8 nvSRAM

Features

Description

High-performance CMOS non-

volatile static RAM 32768 x 8 bits

25 ns Access Times

10 ns Output Enable Access

Times

Software STORE Initiation

Automatic STORE Timing

106 STORE cycles to EEPROM

100 years data retention in

EEPROM

Automatic RECALL on Power Up

Software RECALL Initiation

Unlimited RECALL cycles from

EEPROM

Unlimited Read and Write to

SRAM

Single 5 V ± 10 % Operation

Operating temperature ranges:

0 to 70 °C

-40 to 85 °C

QS 9000 Quality Standard

ESD protection > 2000 V

(MIL STD 883C M3015.7-HBM)

RoHS compliance and Pb- free

Package: SOP28 (330 mil)

The U631H256 has two separate

modes of operation: SRAM mode

and nonvolatile mode. In SRAM

mode, the memory operates as an

ordinary static RAM. In nonvolatile

operation, data is transferred in

parallel from SRAM to EEPROM or

from EEPROM to SRAM. In this

mode SRAM functions are disab-

led.

The U631H256 is a fast static RAM

(25 ns), with a nonvolatile electri-

cally erasable PROM (EEPROM)

element incorporated in each static

memory cell. The SRAM can be

read and written an unlimited num-

ber of times, while independent

nonvolatile data resides in

EEPROM. Data transfers from the

SRAM to the EEPROM (the

STORE operation), or from the

EEPROM to the SRAM (the

RECALL operation) are initiated

through software sequences.

The U631H256 combines the high

performance and ease of use of a

fast SRAM with nonvolatile data

integrity.

Once a STORE cycle is initiated,

further input or output are disabled

until the cycle is completed.

Because a sequence of addresses

is used for STORE initiation, it is

important that no other read or

write accesses intervene in the

sequence or the sequence will be

aborted.

Internally, RECALL is a two step

procedure. First, the SRAM data is

cleared and second, the nonvola-

tile information is transferred into

the SRAM cells.

The RECALL operation in no way

alters the data in the EEPROM

cells. The nonvolatile data can be

recalled an unlimited number of

times.

The U631H256 is pin compatible

with standard SRAMs.

Pin Configuration

A14

A12

A7

A6

A5

A4

A3

A2

A1

A0

DQ0

DQ1

DQ2

VSS

1

2

3

4

5

6

7

8 SOP

9

10

11

12

13

14

28

27

26

25

24

23

22

21

20

19

18

17

16

15

VCC

W

A13

A8

A9

A11

G

A10

E

DQ7

DQ6

DQ5

DQ4

DQ3

Top View

August 15, 2006

STK Control #ML0043

Pin Description

Signal Name

A0 - A14

DQ0 - DQ7

E

G

W

VCC

VSS

Signal Description

Address Inputs

Data In/Out

Chip Enable

Output Enable

Write Enable

Power Supply Voltage

Ground

1 Rev 1.1

1 page

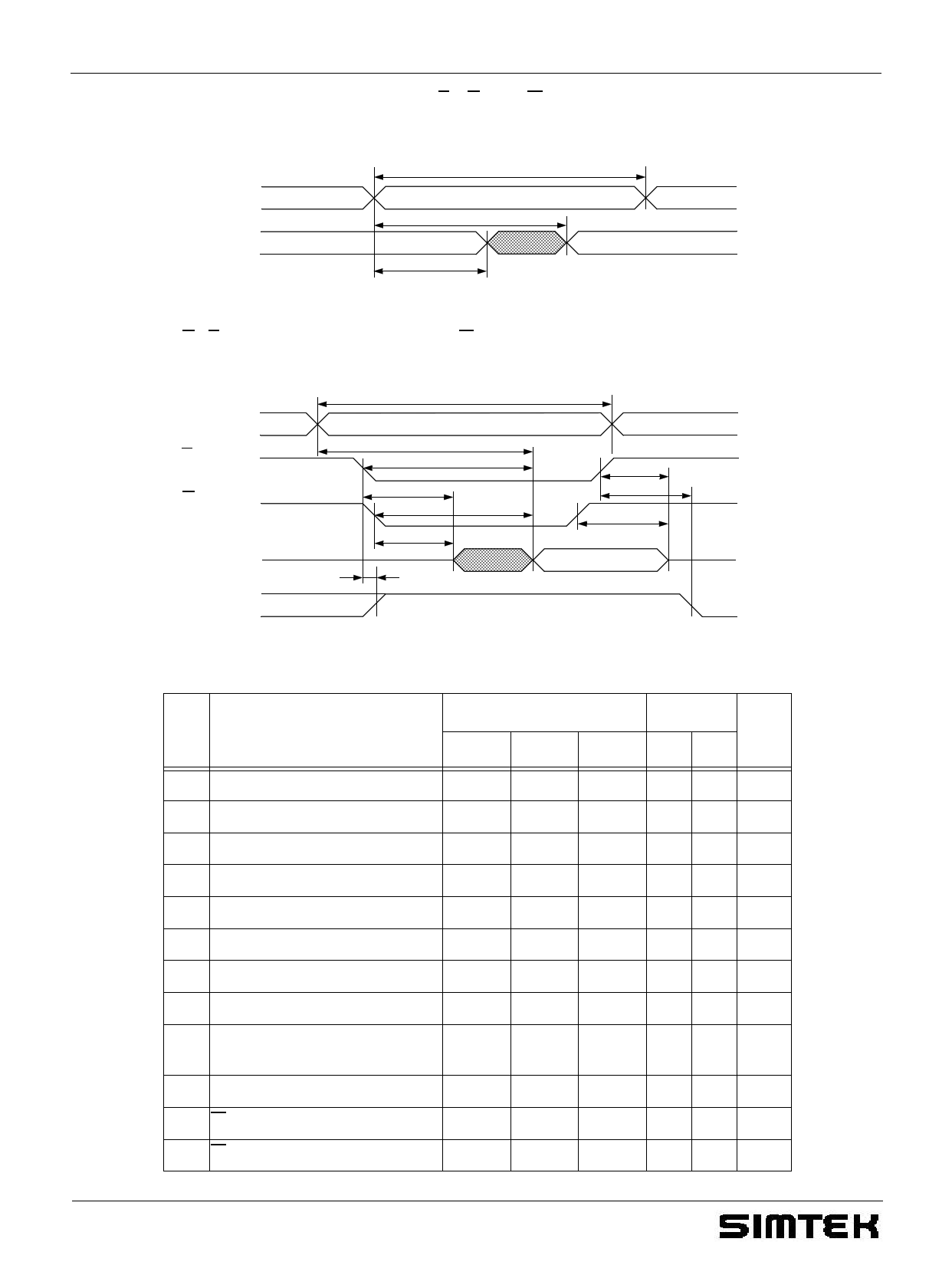

Read Cycle 1: Ai-controlled (during Read cycle: E = G = VIL, W = VIH)f

U631H256

Ai

DQi

Output

Previous Data Valid

tv(A) (9)

tcR (1)

Address Valid

ta(A) (2)

Output Data Valid

Read Cycle 2: G-, E-controlled (during Read cycle: W = VIH)g

Ai

E

G

DQi

Output

ICC

High Impedance

ACTIVE

STANDBY

tcR (1)

Address Valid

ta(A) (2)

ta(E) (3)

ten(E) (7)

ten(G) (8)

ta(G) (4)

tPU (10)

tdis(E) (5)

tPD (11)

tdis(G) (6)

Output Data Valid

No.

Switching Characteristics

Write Cycle

Symbol

Unit

Alt. #1 Alt. #2 IEC Min. Max.

12 Write Cycle Time

13 Write Pulse Width

14 Write Pulse Width Setup Time

tAVAV

tWLWH

15 Address Setup Time

16 Address Valid to End of Write

17 Chip Enable Setup Time

18 Chip Enable to End of Write

tAVWL

tAVWH

tELWH

19 Data Setup Time to End of Write tDVWH

20 Data Hold Time after End of

Write

tWHDX

tAVAV

tWLEH

tAVEL

tAVEH

tELEH

tDVEH

tEHDX

tcW

tw(W)

tsu(W)

tsu(A)

tsu(A-WH)

tsu(E)

tw(E)

tsu(D)

th(D)

25

20

20

0

20

20

20

10

0

ns

ns

ns

ns

ns

ns

ns

ns

ns

21 Address Hold after End of Write tWHAX tEHAX th(A) 0

ns

22 W LOW to Output in High-Zh, i

tWLQZ

tdis(W)

10 ns

23 W HIGH to Output in Low-Z

tWHQX

ten(W)

5

ns

August 15, 2006

STK Control #ML0043

5

Rev 1.1

5 Page

U631H256

RECALL; SRAM operation cannot commence until

tRESTORE after VCC exceeds VSWITCH.

If the U631H256 is in a WRITE state at the end of

power up RECALL, the SRAM data will be corrupted.

To help avoid this situation, a 10 kΩ resistor should be

connected between W and VCC.

Hardware Protection

The U631H256 offers hardware protection against

inadvertent STORE operation through VCC sense.

For VCC < VSWITCH the software initiated STORE ope-

ration will be inhibited.

Low Average Active Power

The U631H256 has been designed to draw significantly

less power when E is LOW (chip enabled) but the

access cycle time is longer than 55 ns.

When E is HIGH the chip consumes only standby cur-

rent.

The overall average current drawn by the part depends

on the following items:

1. CMOS or TTL input levels

2. the time during which the chip is disabled (E HIGH)

3. the cycle time for accesses (E LOW)

4. the ratio of READs to WRITEs

5. the operating temperature

6. the VCC level

The information describes the type of component and shall not be considered as assured characteristics. Terms of

delivery and rights to change design reserved.

August 15, 2006

STK Control #ML0043

11

Rev 1.1

11 Page | ||

| Páginas | Total 13 Páginas | |

| PDF Descargar | [ Datasheet U631H256.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| U631H256 | SoftStore 32K x 8 nvSRAM | Simtek |

| U631H256XS | SoftStore 32K x 8 nvSRAM Die | Simtek |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |