|

|

PDF WED2ZL361MV Data sheet ( Hoja de datos )

| Número de pieza | WED2ZL361MV | |

| Descripción | Synchronous Pipeline Burst NBL SRAM | |

| Fabricantes | White Electronic | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de WED2ZL361MV (archivo pdf) en la parte inferior de esta página. Total 12 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

White Electronic Designs

WED2ZL361MV

1Mx36 Synchronous Pipeline Burst NBL SRAM

FEATURES

Fast clock speed: 166, 150, 133, and 100MHz

Fast access times: 3.5ns, 3.8ns, 4.2ns, and 5.0ns

Fast OE# access times: 3.5ns, 3.8ns, 4.2ns, and

5.0ns

Single +3.3V ± 5% power supply (VCC)

Snooze Mode for reduced-standby power

Individual Byte Write control

Clock-controlled and registered addresses, data

I/Os and control signals

Burst control (interleaved or linear burst)

Packaging:

• 119-bump BGA package

Low capacitive bus loading

This product is subject to change without notice.

DESCRIPTION

The WEDC SyncBurst — SRAM family employs high-

speed, low-power CMOS designs that are fabricated

using an advanced CMOS process. WEDC’s 32Mb

SyncBurst SRAMs integrate two 1M x 18 SRAMs into a

single BGA package to provide 1M x 36 configuration. All

synchronous inputs pass through registers controlled by

a positive-edge-triggered single-clock input (CLK). The

NBL or No Bus Latency Memory utilizes all the bandwidth

in any combination of operating cycles. Address, data

inputs, and all control signals except output enable and

linear burst order are synchronized to input clock. Burst

order control must be tied “High or Low.” Asynchronous

inputs include the sleep mode enable (ZZ). Output Enable

controls the outputs at any given time. Write cycles are

internally self-timed and initiated by the rising edge of the

clock input. This feature eliminates complex off-chip write

pulse generation and provides increased timing flexibility

for incoming signals.

FIGURE 1 – PIN CONFIGURATION

(Top View)

Block Diagram

1234567

A VCC SA SA SA SA SA VCC

B SA CE2 SA ADV# SA CE2# NC

C NC SA SA VCC SA SA NC

D DQC DQPC VSS NC VSS DQPB DQB

E DQC DQC VSS CE1# VSS DQB DQB

F VCC DQC VSS OE# VSS DQB VCC

G DQC DQC BWC# SA BWB# DQB DQB

H DQC DQC VSS WE# VSS DQB DQB

J VCC VCC NC VCC NC VCC VCC

K DQD DQD VSS CLK VSS DQA DQA

L DQD DQD BWD# NC BWA# DQA DQA

M VCC DQD VSS CKE# VSS DQA VCC

N DQD DQD VSS SA1 VSS DQA DQA

P DQD DQPD VSS SA0 VSS DQPA DQA

R NC SA LBO VCC NC SA NC

T NC NC SA SA SA NC ZZ

U VCC NC NC NC NC NC VCC

CLK

CKE#

ADV#

LBO#

CE1#

CE2

CE2#

OE#

WE#

ZZ

1M x 18

CLK

CKE#

ADV#

LBO#

CS1#

CS2

CS2#

OE#

WE#

ZZ

1M x 18

CLK

CKE#

ADV#

LBO#

CS1#

CS2

CS2#

OE#

WE#

ZZ

Address Bus

(SA0 - SA19)

DQc, DQd

DQPc, DQPd

DQa, DQb

DQPa, DQPb

DQa - DQd

DQPa - DQPd

June 2004

Rev. 3

1 White Electronic Designs Corporation • (602) 437-1520 • www.wedc.com

1 page

White Electronic Designs

WED2ZL361MV

AC Characteristics

Parameter

Clock Time

Clock Access Time

Output enable to Data Valid

Clock High to Output Low-Z

Output Hold from Clock High

Output Enable Low to output Low-Z

Output Enable High to Output High-Z

Clock High to Output High-Z

Clock High Pulse Width

Clock Low Pulse Width

Address Setup to Clock High

CKE Setup to Clock High

Data Setup to Clock High

Write Setup to Clock High

Address Advance to Clock High

Chip Select Setup to Clock High

Address Hold to Clock high

CKE Hold to Clock High

Data Hold to Clock High

Write Hold to Clock High

Address Advance to Clock High

Chip Select Hold to Clock High

Symbol

TCYC

tCD

tOE

tLZC

tOH

tLZOE

tHZOE

tHZC

tCH

tCL

tAS

tCES

tDS

tWS

tADVS

tCSS

tAH

tCEH

tDH

tWH

tADVH

tCSH

166MHz

Min Max

6.0

— 3.5

— 3.5

1.5 —

1.5 —

0.0 —

— 3.0

— 3.0

2.2 —

2.2 —

1.5 —

1.5 —

1.5 —

1.5 —

1.5 —

1.5 —

0.5 —

0.5 —

0.5 —

0.5 —

0.5 —

0.5 —

150MHz

Min Max

6.7

— 3.8

— 3.8

1.5 —

1.5 —

0.0 —

— 3.0

— 3.0

2.5 —

2.5 —

1.5 —

1.5 —

1.5 —

1.5 —

1.5 —

1.5 —

0.5 —

0.5 —

0.5 —

0.5 —

0.5 —

0.5 —

133MHz

Min Max

7.5

— 4.2

— 4.2

1.5 —

1.5 —

0.0 —

— 3.5

— 3.5

3.0 —

3.0 —

1.5 —

1.5 —

1.5 —

1.5 —

1.5 —

1.5 —

0.5 —

0.5 —

0.5 —

0.5 —

0.5 —

0.5 —

100MHz

Min Max

10.0

— 5.0

— 5.0

1.5 —

1.5 —

0.0 —

— 3.5

— 3.5

3.0 —

3.0 —

1.5 —

1.5 —

1.5 —

1.5 —

1.5 —

1.5 —

0.5 —

0.5 —

0.5 —

0.5 —

0.5 —

0.5 —

Units

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

NOTES:

1. All Address inputs must meet the specified setup and hold times for all rising clock

(CLK) edges when ADV# is sampled low and CEx# is sampled valid. All other

synchronous inputs must meet the specified setup and hold times whenever this

device is chip selected.

2. Chip enable must be valid at each rising edge of CLK (when ADV# is Low) to remain

enabled.

3. A write cycle is defined by WE# low having been registered into the device at ADV

Low. A Read cycle is defined by WE# High with ADV# Low. Both cases must meet

setup and hold times.

AC Test Conditions

VSS = 0V, = 0°C ≤ TA ≤ +70°C, VCC = 3.3V ± 5%; Commercial or -40°C ≤ TA ≤ +85°C, VCC = 3.3V ± 5%; Industrial

Parameter

Input Pulse Level

Input Rise and Fall Time (Measured at 20% to 80%)

Input and Output Timing Reference Levels

Output Load

Value

0 to 3.0V

1.0V/ns

1.5V

See Output Load (A)

Output Load (A)

DOUT

Zo=50Ω

RL=50Ω

30pF*

VL=1.5V

*Including Scope and Jig Capacitance

Output Load (B)

for a tLZC, tLZOE, tHZOE, and tHZC

+3.3V

DOUT

3.9 Ω

353 Ω

5pF*

June 2004

Rev. 3

5 White Electronic Designs Corporation • (602) 437-1520 • www.wedc.com

5 Page

White Electronic Designs

WED2ZL361MV

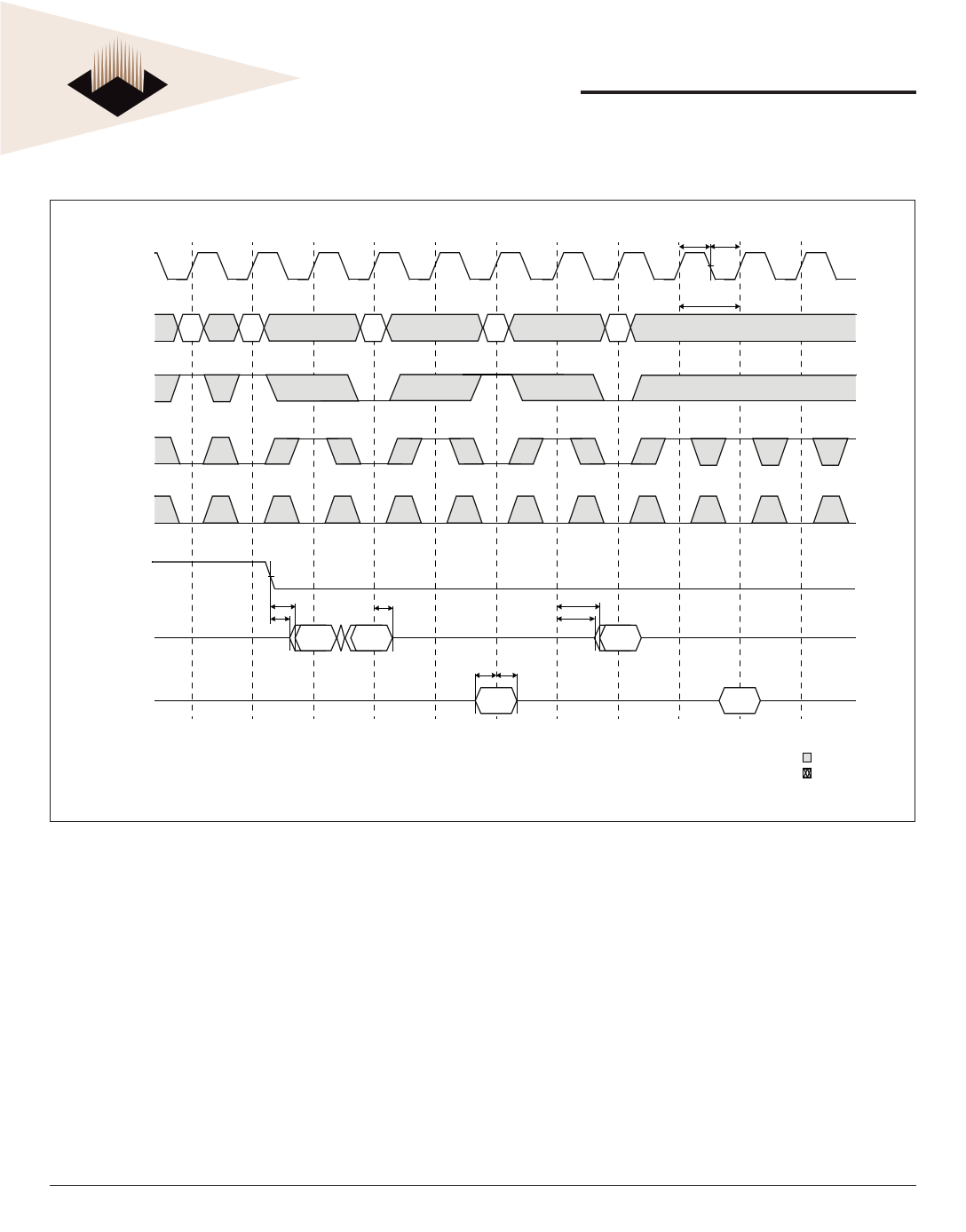

FIGURE 7 – TIMING WAVEFORM OF CE# OPERATION

Clock

tCH tCL

tCYC

Address

A1

A2

A3

A4

A5

WRITE#

CEx#

ADV

OE#

Data Out

tOE

tLZOE

Q1

tHZC

Q2

Data In

NOTES: WRITE# = L means WE = L, and BWx# = L

CEx# refers to the combination of CE1#, CE2 and CE2#.

tCD

tLZC

tDS tDH

D3

Q4

D5

Don't Care

Undefined

June 2004

Rev. 3

11 White Electronic Designs Corporation • (602) 437-1520 • www.wedc.com

11 Page | ||

| Páginas | Total 12 Páginas | |

| PDF Descargar | [ Datasheet WED2ZL361MV.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| WED2ZL361MS | Synchronous Pipeline Burst NBL SRAM | White Electronic |

| WED2ZL361MV | Synchronous Pipeline Burst NBL SRAM | White Electronic |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |