|

|

PDF CY14B101MA Data sheet ( Hoja de datos )

| Número de pieza | CY14B101MA | |

| Descripción | 1-Mbit (128K x 8/64K x 16) nvSRAM | |

| Fabricantes | Cypress Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de CY14B101MA (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

CY14B101KA

CY14B101MA

1-Mbit (128K × 8/64K × 16) nvSRAM with

Real Time Clock

1-Mbit (128K × 8/64K × 16) nvSRAM with Real Time Clock

Features

■ 1-Mbit nonvolatile static random access memory (nvSRAM)

❐ 25 ns and 45 ns access times

❐ Internally organized as 128K × 8 (CY14B101KA) or 64K × 16

(CY14B101MA)

❐ Hands off automatic STORE on power-down with only a small

capacitor

❐ STORE to QuantumTrap nonvolatile elements is initiated by

software, hardware, or AutoStore on power-down

❐ RECALL to SRAM initiated on power-up or by software

■ High reliability

❐ Infinite Read, Write, and RECALL cycles

❐ 1 million STORE cycles to QuantumTrap

❐ 20 year data retention

■ Real time clock (RTC)

❐ Full featured real time clock

❐ Watchdog timer

❐ Clock alarm with programmable interrupts

❐ Capacitor or battery backup for RTC

❐ Backup current of 0.35 µA (Typ)

■ Industry standard configurations

❐ Single 3 V +20%, –10% operation

❐ Industrial temperature

■ Packages

❐ 44-/54-pin thin small outline package (TSOP) Type II

❐ 48-pin shrink small outline package (SSOP)

■ Pb-free and restriction of hazardous substances (RoHS)

compliant

Functional Description

The Cypress CY14B101KA/CY14B101MA combines a 1-Mbit

nvSRAM with a full featured real time clock in a monolithic

integrated circuit. The embedded nonvolatile elements

incorporate QuantumTrap technology producing the world’s

most reliable nonvolatile memory. The SRAM is read and written

an infinite number of times, while independent nonvolatile data

resides in the nonvolatile elements.

The real time clock function provides an accurate clock with leap

year tracking and a programmable, high accuracy oscillator. The

alarm function is programmable for periodic minutes, hours,

days, or months alarms. There is also a programmable watchdog

timer for process control.

For a complete list of related documentation, click here.

Logic Block Diagram[1, 2, 3]

A5

A6

A7

A8

A9

A12

A13

A14

A15

A16

R

O

W

D

E

C

O

D

E

R

Quatrum

Trap

1024 X 1024

STORE

RECALL

STATIC RAM

ARRAY

1024 X 1024

VCC

VCA

P

POWER

CONTROL

STORE/RECALL

CONTROL

SOFTWARE

DETECT

VRTCbat

VRTCcap

HSB

A14 - A2

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

I

N

P

U

T

B COLUMN I/O

U

F

F

E

R COLUMN DEC

S

A0 A1 A2 A3 A4 A10 A11

RTC

MUX

Xout

Xin

INT

A16- A0

OE

WE

CE

BLE

BHE

Notes

1. Address A0–A16 for × 8 configuration and Address A0–A15 for × 16 configuration.

2. Data DQ0–DQ7 for × 8 configuration and Data DQ0–DQ15 for × 16 configuration.

3. BHE and BLE are applicable for × 16 configuration only.

Cypress Semiconductor Corporation • 198 Champion Court

Document Number: 001-42880 Rev. *O

• San Jose, CA 95134-1709 • 408-943-2600

Revised February 22, 2016

1 page

CY14B101KA

CY14B101MA

Device Operation

The CY14B101KA/CY14B101MA nvSRAM is made up of two

functional components paired in the same physical cell. These

are a SRAM memory cell and a nonvolatile QuantumTrap cell.

The SRAM memory cell operates as a standard fast static RAM.

Data in the SRAM is transferred to the nonvolatile cell (the

STORE operation), or from the nonvolatile cell to the SRAM (the

RECALL operation). Using this unique architecture, all cells are

stored and recalled in parallel. During the STORE and RECALL

operations SRAM read and write operations are inhibited. The

CY14B101KA/CY14B101MA supports infinite reads and writes

similar to a typical SRAM. In addition, it provides infinite RECALL

operations from the nonvolatile cells and up to 1 million STORE

operations. See Truth Table for SRAM Operations on page 28 for

a complete description of read and write modes.

SRAM Read

The CY14B101KA/CY14B101MA performs a read cycle

whenever CE and OE are LOW, and WE and HSB are HIGH.

The address specified on pins A0–16 or A0–15 determines which

of the 131,072 data bytes or 65,536 words of 16 bits each are

accessed. Byte enables (BHE, BLE) determine which bytes are

enabled to the output, in the case of 16-bit words. When the read

is initiated by an address transition, the outputs are valid after a

delay of tAA (read cycle #1). If the read is initiated by CE or OE,

the outputs are valid at tACE or at tDOE, whichever is later (read

cycle #2). The data output repeatedly responds to address

changes within the tAA access time without the need for

transitions on any control input pins. This remains valid until

another address change or until CE or OE is brought HIGH, or

WE or HSB is brought LOW.

SRAM Write

A write cycle is performed when CE and WE are LOW and HSB

is HIGH. The address inputs must be stable before entering the

write cycle and must remain stable until CE or WE goes HIGH at

the end of the cycle. The data on the common I/O pins IO0–7 are

written into the memory if it is valid tSD before the end of a

WE-controlled write, or before the end of an CE-controlled write.

The Byte Enable inputs (BHE, BLE) determine which bytes are

written, in the case of 16-bit words. It is recommended that OE

be kept HIGH during the entire write cycle to avoid data bus

contention on common I/O lines. If OE is left LOW, internal

circuitry turns off the output buffers tHZWE after WE goes LOW.

AutoStore Operation

The CY14B101KA/CY14B101MA stores data to the nvSRAM

using one of three storage operations. These three operations

are: Hardware STORE, activated by the HSB; Software STORE,

activated by an address sequence; AutoStore, on device

power-down. The AutoStore operation is a unique feature of

QuantumTrap technology and is enabled by default on the

CY14B101KA/CY14B101MA.

During a normal operation, the device draws current from VCC to

charge a capacitor connected to the VCAP pin. This stored

charge is used by the chip to perform a single STORE operation.

If the voltage on the VCC pin drops below VSWITCH, the part

automatically disconnects the VCAP pin from VCC. A STORE

operation is initiated with power provided by the VCAP capacitor.

Note If the capacitor is not connected to VCAP pin, AutoStore

must be disabled using the soft sequence specified in Preventing

AutoStore on page 8. In case AutoStore is enabled without a

capacitor on VCAP pin, the device attempts an AutoStore

operation without sufficient charge to complete the Store. This

corrupts the data stored in nvSRAM.

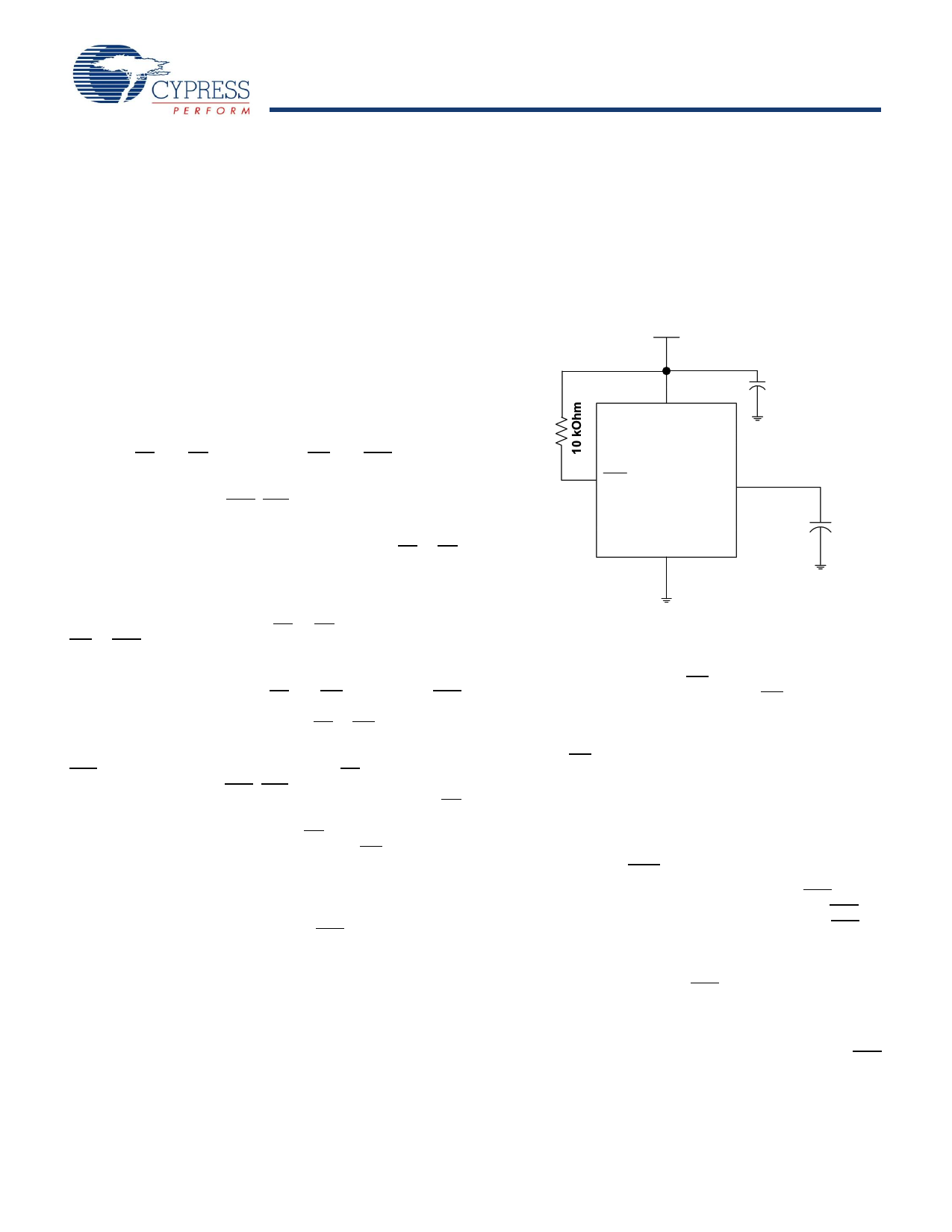

Figure 2. AutoStore Mode

VCC

0.1 uF

VCC

WE VCAP

VSS

VCAP

Figure 2 shows the proper connection of the storage capacitor

(VCAP) for automatic STORE operation. See DC Electrical

Characteristics on page 18 for the size of the VCAP. The voltage

on the VCAP pin is driven to VCC by a regulator on the chip. A

pull-up should be placed on WE to hold it inactive during

power-up. This pull-up is only effective if the WE signal is tristate

during power-up. Many MPUs tristate their controls on power-up.

This should be verified when using the pull-up. When the

nvSRAM comes out of power-on-RECALL, the MPU must be

active or the WE held inactive until the MPU comes out of reset.

To reduce unnecessary nonvolatile stores, AutoStore and

Hardware STORE operations are ignored unless at least one

write operation has taken place since the most recent STORE or

RECALL cycle. Software initiated STORE cycles are performed

regardless of whether a write operation has taken place.

Hardware STORE (HSB) Operation

The CY14B101KA/CY14B101MA provides the HSB pin to

control and acknowledge the STORE operations. The HSB pin

is used to request a Hardware STORE cycle. When the HSB pin

is driven LOW, the CY14B101KA/CY14B101MA conditionally

initiates a STORE operation after tDELAY. An actual STORE cycle

begins only if a write to the SRAM has taken place since the last

STORE or RECALL cycle. The HSB pin also acts as an open

drain driver (internal 100 k weak pull-up resistor) that is

internally driven LOW to indicate a busy condition when the

STORE (initiated by any means) is in progress.

Note After each Hardware and Software STORE operation HSB

is driven HIGH for a short time (tHHHD) with standard output high

current and then remains HIGH by internal 100 k pull-up

resistor.

Document Number: 001-42880 Rev. *O

Page 5 of 37

5 Page

CY14B101KA

CY14B101MA

mode is used as an interrupt to a host microcontroller. The

control bits are summarized in the following section.

Interrupts are only generated while working on normal power and

are not triggered when system is running in backup power mode.

Note CY14B101KA generates valid interrupts only after the

Power-up RECALL sequence is completed. All events on INT pin

must be ignored for tHRECALL duration after power-up.

Interrupt Register

Watchdog Interrupt Enable (WIE). When set to ‘1’, the

watchdog timer drives the INT pin and an internal flag when a

watchdog time out occurs. When WIE is set to ‘0’, the watchdog

timer only affects the WDF flag in Flags register .

Alarm Interrupt Enable (AIE). When set to ‘1’, the alarm match

drives the INT pin and an internal flag. When AIE is set to ‘0’, the

alarm match only affects the AF flag in Flags register .

Power Fail Interrupt Enable (PFE). When set to ‘1’, the power

fail monitor drives the pin and an internal flag. When PFE is set

to ‘0’, the power fail monitor only affects the PF flag in flags

register.

High/Low (H/L). When set to a ‘1’, the INT pin is active HIGH

and the driver mode is push pull. The INT pin drives HIGH only

when VCC is greater than VSWITCH. When set to a ‘0’, the INT pin

is active LOW and the drive mode is open drain. The INT pin

must be pulled up to Vcc by a 10 k resistor while using the

interrupt in active LOW mode.

Pulse/Level (P/L). When set to a ‘1’ and an interrupt occurs, the

INT pin is driven for approximately 200 ms. When P/L is set to a

‘0’, the INT pin is driven HIGH or LOW (determined by H/L) until

the flags register is read.

When an enabled interrupt source activates the INT pin, an

external host reads the flags registers to determine the cause.

All flags are cleared when the register is read. If the INT pin is

programmed for level mode, then the condition clears and the

INT pin returns to its inactive state. If the pin is programmed for

pulse mode, then reading the flag also clears the flag and the pin.

The pulse does not complete its specified duration if the flags

register is read. If the INT pin is used as a host reset, then the

flags register is not read during a reset.

Flags Register

The flags register has three flag bits: WDF, AF, and PF, which

can be used to generate an interrupt. These flags are set by the

watchdog timeout, alarm match, or power fail monitor

respectively. The processor can either poll this register or enable

interrupts to be informed when a flag is set. These flags are

automatically reset when the register is read. The flags register

is automatically loaded with the value 0x00 on power-up (except

for the OSCF bit; see Stopping and Starting the Oscillator on

page 9).

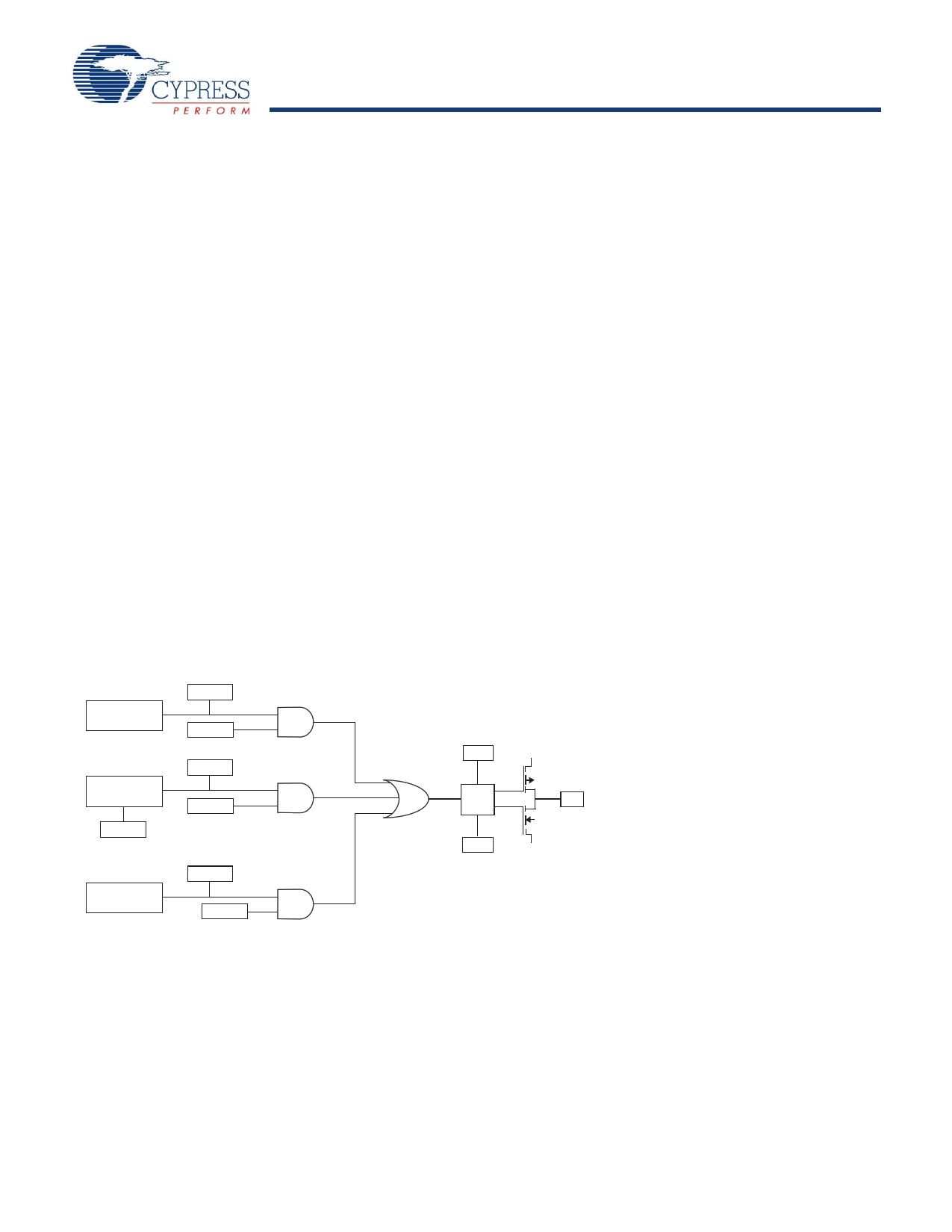

Figure 4. Interrupt Block Diagram

Watchdog

Timer

Power

Monitor

VINT

Clock

Alarm

WDF

WIE

PF

PFE

AF

AIE

P/L VCC

Pin

Driver

H/L VSS

INT

WDF - Watchdog Timer Flag

WIE - Watchdog Interrupt

Enable

PF - Power Fail Flag

PFE - Power Fail Enable

AF - Alarm Flag

AIE - Alarm Interrupt Enable

P/L - Pulse Level

H/L - High/Low

Document Number: 001-42880 Rev. *O

Page 11 of 37

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet CY14B101MA.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| CY14B101MA | 1-Mbit (128K x 8/64K x 16) nvSRAM | Cypress Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |