|

|

PDF 74ACT373M Data sheet ( Hoja de datos )

| Número de pieza | 74ACT373M | |

| Descripción | OCTAL D-TYPE LATCH WITH 3 STATE OUTPUT NON INVERTING | |

| Fabricantes | STMicroelectronics | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de 74ACT373M (archivo pdf) en la parte inferior de esta página. Total 10 Páginas | ||

|

No Preview Available !

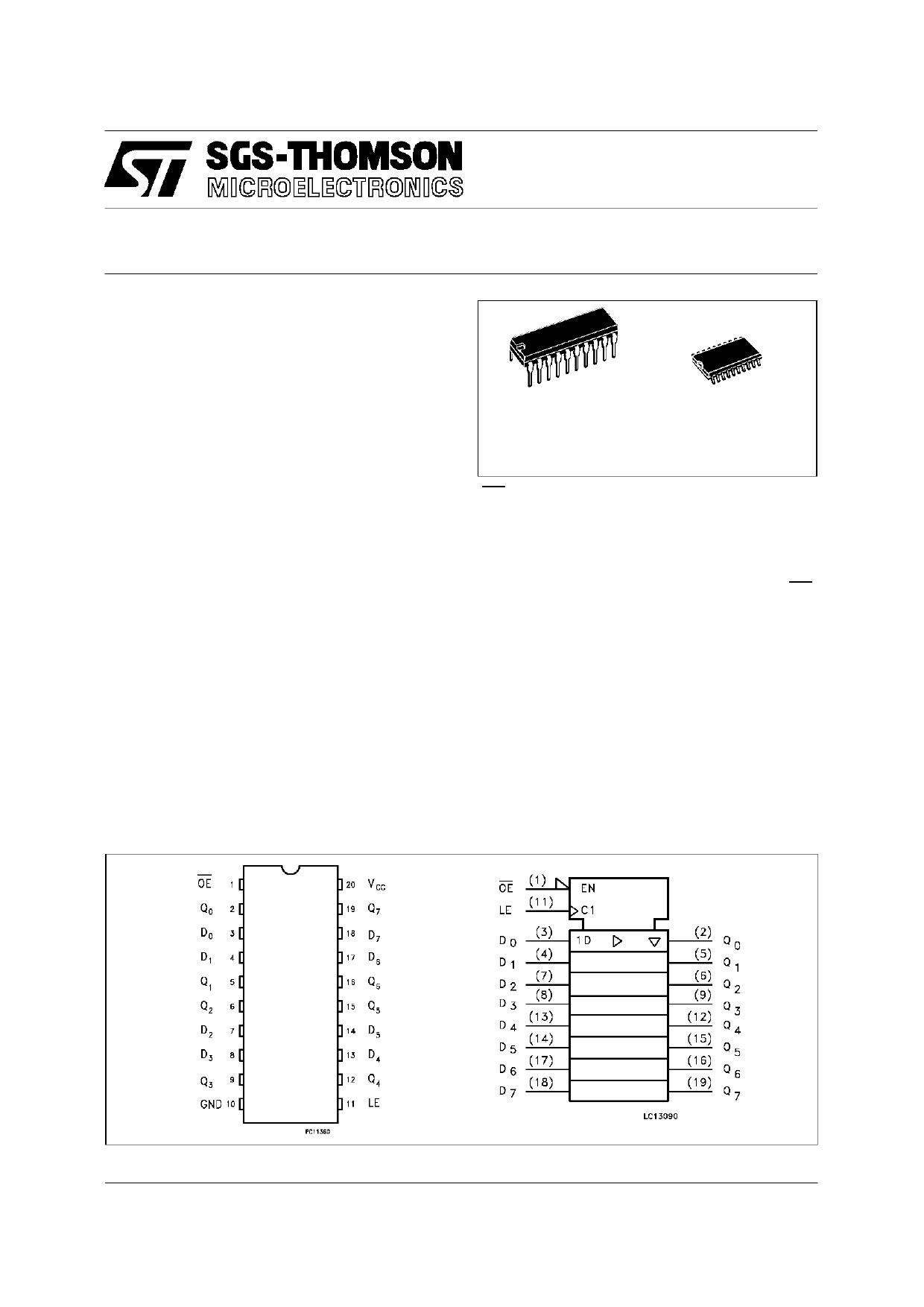

74ACT373

OCTAL D-TYPE LATCH

WITH 3 STATE OUTPUT NON INVERTING

s HIGH SPEED: tPD = 6 ns (TYP.) at VCC = 5V

s LOW POWER DISSIPATION:

ICC = 8 µA (MAX.) at TA = 25 oC

s COMPATIBLE WITH TTL OUTPUTS

VIH = 2V (MIN), VIL = 0.8V (MAX)

s 50Ω TRANSMISSION LINE DRIVING

CAPABILITY

s SYMMETRICAL OUTPUT IMPEDANCE:

|IOH| = IOL = 24 mA (MIN)

s BALANCED PROPAGATION DELAYS:

tPLH ≅ tPHL

s OPERATING VOLTAGE RANGE:

VCC (OPR) = 4.5V to 5.5V

s PIN AND FUNCTION COMPATIBLE WITH

74 SERIES 373

s IMPROVED LATCH-UP IMMUNITY

DESCRIPTION

The ACT373 is an advanced high-speed CMOS

OCTAL D-TYPE LATCH with 3 STATE OUTPUT

NON INVERTING fabricated with sub-micron

silicon gate and double-layer metal wiring C2MOS

technology. It is ideal for low power applications

mantaining high speed operation similar to

equivalent Bipolar Schottky TTL.

These 8 bit D-Type latch are controlled by a latch

enable input (LE) and an output enable input

BM

(Plastic Package)

(Micro Package)

ORDER CODES :

74ACT373B

74ACT373M

(OE).

While the LE inputs is held at a high level, the Q

outputs will follow the data input precisely or

inversely. When the LE is taken low, the Q

outputs will be latched precisely or inversely at

the logic level of D input data. While the (OE)

input is low, the 8 outputs will be in a normal logic

state (high or low logic level) and while high level

the outputs will be in a high impedance state.

This device is designed to interface directly High

Speed CMOS systems with TTL and NMOS

components.

All inputs and outputs are equipped with

protection circuits against static discharge, giving

them 2KV ESD immunity and transient excess

voltage.

PIN CONNECTION AND IEC LOGIC SYMBOLS

April 1997

1/10

1 page

74ACT373

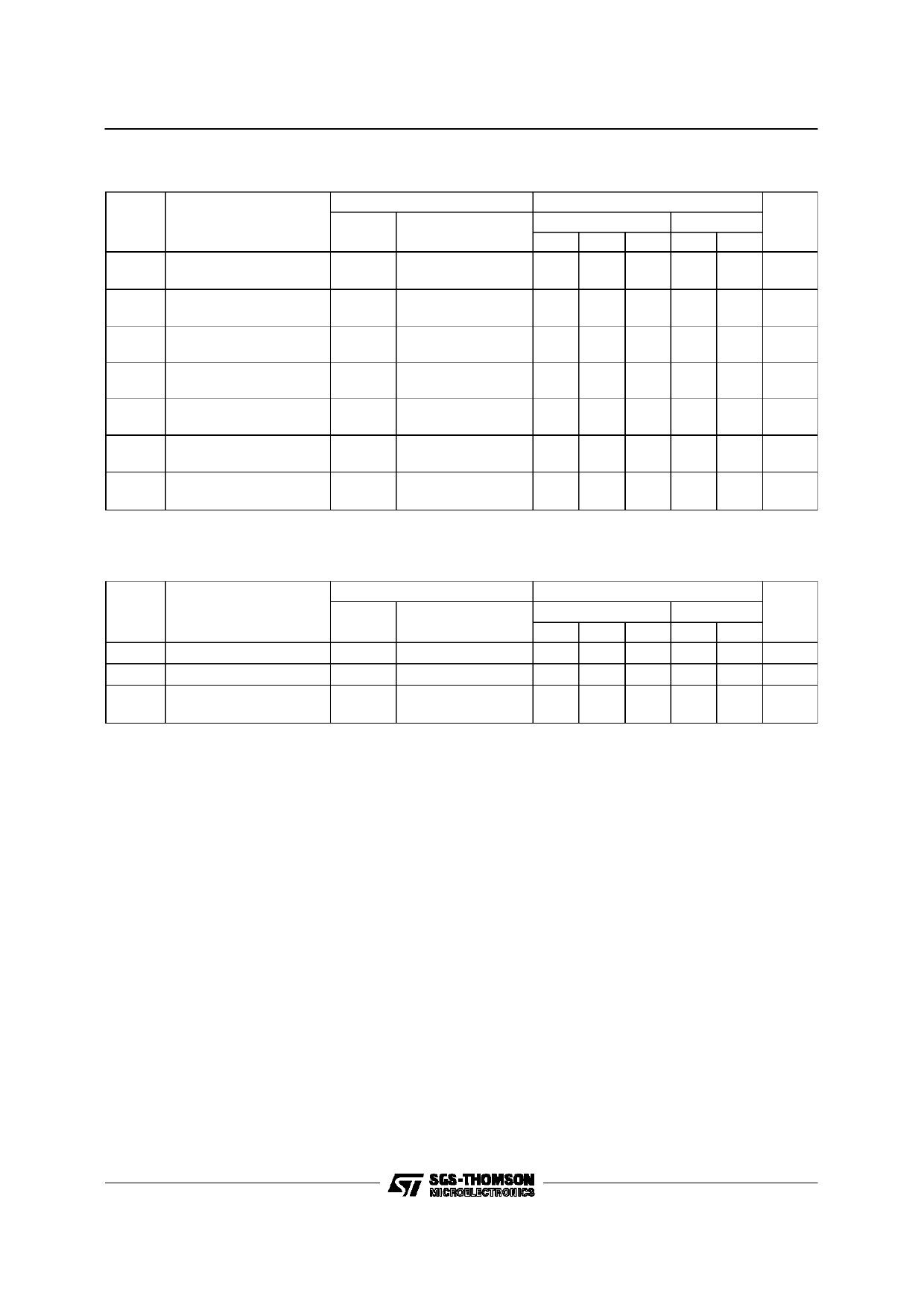

AC ELECTRICAL CHARACTERISTICS (CL = 50 pF, RL = 500 Ω, Input tr = tf =3 ns)

Symbol

P ar ame te r

tPLH Propagation Delay Time

tPHL LE to Q

tPLH Propagation Delay Time

tPHL D to Q

tPZL Output Enable Time

tPZH

tPLH Output Disable Time

tPHL

tw CK Pulse Width, HIGH

or LOW

ts Setup Time Q to CK

HIGH or LOW

th Hold Time Q to CK

HIGH or LOW

(*) Voltage range is 5V ± 0.5V

Test Condition

V CC

(V)

5.0(*)

5.0(*)

5.0(*)

5.0(*)

5.0(*)

5.0(*)

5.0(*)

Value

TA = 25 oC

-40 to 85 oC

Min. Typ. Max. Min. Max.

6.0 10.0

11.5

Unit

ns

5.5 10.0

11.5 ns

6.0 9.5

10.5 ns

7.0 11.0

12.5 ns

1.0 7.0

8.0 ns

0.5 7.0

8.0 ns

0.5 0.0

1.0 ns

CAPACITIVE CHARACTERISTICS

Symbol

P ar ame te r

Test Conditions

V CC

(V)

Value

TA = 25 oC

-40 to 85 oC

Min. Typ. Max. Min. Max.

Unit

COUT Output Capacitance

5.0

10 pF

CIN Input Capacitance

5.0

5 pF

CPD Power Dissipation

Capacitance (note 1)

5.0

25 pF

1) CPD is defined as the value of the IC’s internal equivalent capacitance which is calculated from the operating current consumption without load. (Refer to

Test Circuit). Average operating current can be obtained by the following equation. ICC(opr) = CPD • VCC • fIN + ICC/n (per circuit)

5/10

5 Page | ||

| Páginas | Total 10 Páginas | |

| PDF Descargar | [ Datasheet 74ACT373M.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| 74ACT373 | OCTAL D-TYPE LATCH WITH 3 STATE OUTPUT NON INVERTING | STMicroelectronics |

| 74ACT373B | OCTAL D-TYPE LATCH WITH 3 STATE OUTPUT NON INVERTING | STMicroelectronics |

| 74ACT373M | OCTAL D-TYPE LATCH WITH 3 STATE OUTPUT NON INVERTING | STMicroelectronics |

| 74ACT373MSA | Octal Transparent Latch with 3-STATE Outputs | Fairchild Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |