|

|

PDF 74ALVC16374 Data sheet ( Hoja de datos )

| Número de pieza | 74ALVC16374 | |

| Descripción | Low-Voltage 1.8/2.5/3.3V 16-Bit D-Type Flip-Flop | |

| Fabricantes | ON Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de 74ALVC16374 (archivo pdf) en la parte inferior de esta página. Total 11 Páginas | ||

|

No Preview Available !

74ALVC16374

Low−Voltage 1.8/2.5/3.3 V

16−Bit D−Type Flip−Flop

With 3.6 V−Tolerant Inputs and Outputs

(3−State, Non−Inverting)

The 74ALVC16374 is an advanced performance, non−inverting

16−bit D−type flip−flop. It is designed for very high−speed, very

low−power operation in 1.8 V, 2.5 V or 3.3 V systems. The

ALVC16374 is byte controlled, with each byte functioning identically,

but independently. Each byte has separate Output Enable and Clock

Pulse inputs. These control pins can be tied together for a full 16−bit

operation.

The 74ALVC16374 consists of 16 edge−triggered flip−flops with

individual D−type inputs and 3.6 V−tolerant 3−state outputs. The

clocks (CPn) and Output Enables (OEn) are common to all flip−flops

within the respective byte. The flip−flops will store the state of

individual D inputs that meet the setup and hold time requirements on

the LOW−to−HIGH Clock (CP) transition. With the OE LOW, the

contents of the flip−flops are available at the outputs. When the OE is

HIGH, the outputs go to the high impedance state. The OE input level

does not affect the operation of the flip−flops.

• Designed for Low Voltage Operation: VCC = 1.65−3.6 V

• 3.6 V Tolerant Inputs and Outputs

• High Speed Operation: 3.6 ns max for 3.0 to 3.6 V

4.5 ns max for 2.3 to 2.7 V

7.8 ns max for 1.65 to 1.95 V

• Static Drive: ±24 mA Drive at 3.0 V

±12 mA Drive at 2.3 V

±4 mA Drive at 1.65 V

• Supports Live Insertion and Withdrawal

• IOFF Specification Guarantees High Impedance When VCC = 0 V†

• Near Zero Static Supply Current in All Three Logic States (40 mA)

Substantially Reduces System Power Requirements

• Latchup Performance Exceeds ±250 mA @ 125°C

• ESD Performance: Human Body Model >2000 V; Machine Model

>200 V

• Second Source to Industry Standard 74ALVC16374

†To ensure the outputs activate in the 3−state condition, the output enable pins

should be connected to VCC through a pull−up resistor. The value of the resistor is

determined by the current sinking capability of the output connected to the OE pin.

http://onsemi.com

MARKING DIAGRAM

48

48

1

TSSOP−48

DT SUFFIX

CASE 1201

74ALVC16374DT

AWLYYWW

1

A = Assembly

Location

WL = Wafer Lot

YY = Year

WW = Work Week

PIN NAMES

Pins

Function

OEn

CPn

D0−D15

O0−O15

Output Enable Inputs

Clock Pulse Inputs

Inputs

Outputs

ORDERING INFORMATION

Device

Package

Shipping

74ALVC16374DTR TSSOP 2500/Tape & Reel

© Semiconductor Components Industries, LLC, 2006

June, 2006 − Rev. 1

1

Publication Order Number:

74ALVC16374/D

1 page

74ALVC16374

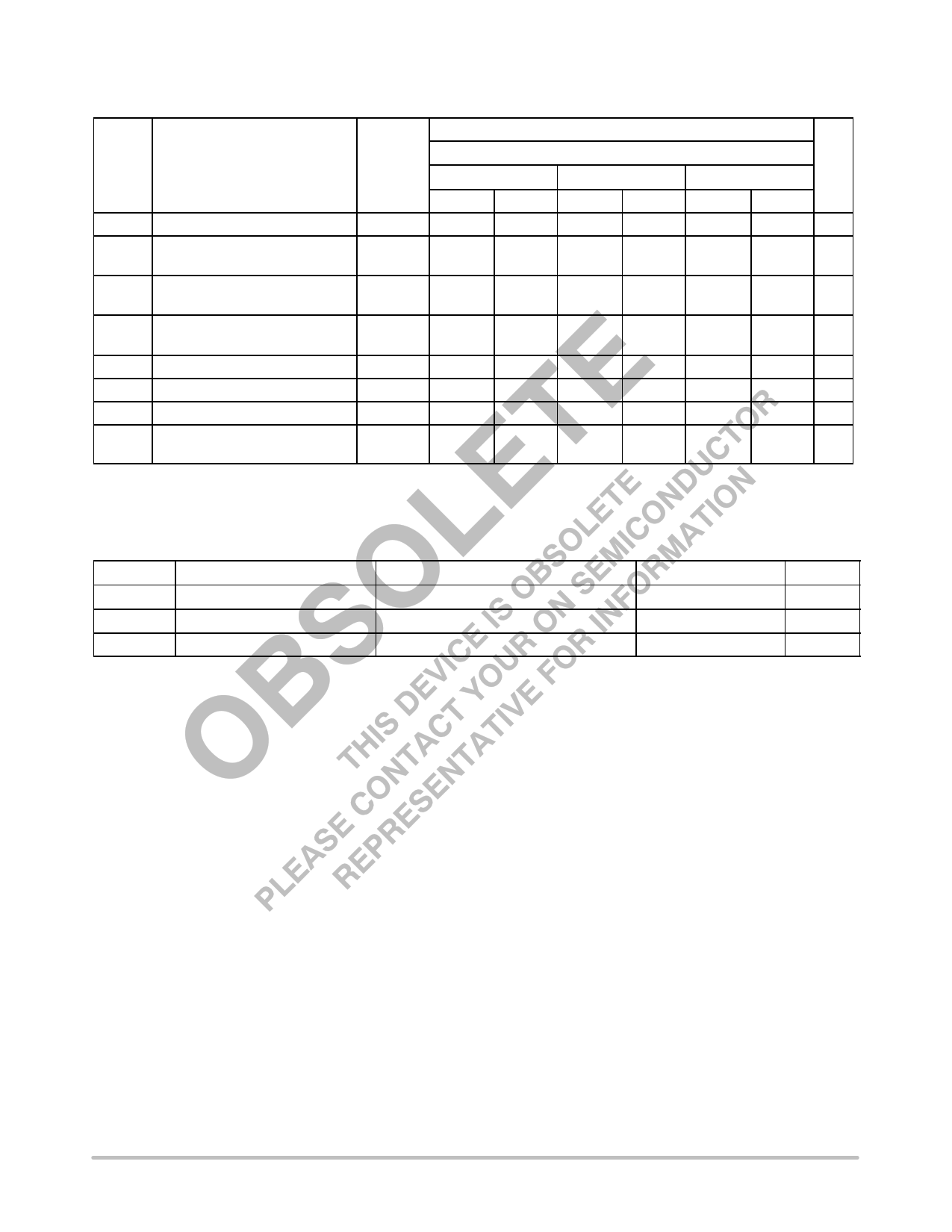

AC CHARACTERISTICS (Note 10; tR = tF = 2.0 ns; CL = 30 pF; RL = 500 W)

Limits

Symbol

Parameter

Waveform

VCC = 3.0 V to 3.6 V

Min Max

TA = −40°C to +85°C

VCC = 2.3 V to 2.7 V

Min Max

VCC = 1.65 to 1.95 V

Min Max

Unit

fmax Clock Pulse Frequency

1 250

200

100 MHz

tPLH Propagation Delay

tPHL

CP to On

1 1.1 3.6 1.0 4.5 1.5 7.8 ns

1.1 3.6 1.0 4.5 1.5 7.8

tPZH

tPZL

Output Enable Time to

High and Low Level

2 1.0 4.7 1.0 6.0 1.5 9.2 ns

1.0 4.7 1.0 6.0 1.5 9.2

tPHZ

tPLZ

Output Disable Time From

High and Low Level

2 1.4 4.1 1.2 5.1 1.5 6.8 ns

1.4 4.1 1.2 5.1 1.5 6.8

ts

Setup Time, High or Low Dn to CP

3

1.1

1.0

2.5 ns

th

Hold Time, High or Low Dn to CP

3

1.4

1.5

1.0 ns

tw CP Pulse Width, High 3 3.3 3.3 4.0 ns

tOSHL

tOSLH

Output−to−Output Skew

(Note 11)

0.5 0.5 0.75 ns

0.5 0.5 0.75

10. For CL = 50 pF, add approximately 300 ps to the AC maximum specification.

11. Skew is defined as the absolute value of the difference between the actual propagation delay for any two separate outputs of the same device.

The specification applies to any outputs switching in the same direction, either HIGH−to−LOW (tOSHL) or LOW−to−HIGH (tOSLH); parameter

guaranteed by design.

CAPACITIVE CHARACTERISTICS

Symbol

Parameter

CIN Input Capacitance

COUT

Output Capacitance

CPD Power Dissipation Capacitance

12. VCC = 1.8, 2.5 or 3.3 V; VI = 0 V or VCC.

Condition

Note 12

Note 12

Note 12, 10MHz

Typical

6

7

20

Unit

pF

pF

pF

http://onsemi.com

5

5 Page

74ALVC16374

PACKAGE DIMENSIONS

48

L

1

PIN 1

IDENT.

D

0.076 (0.003)

−T− SEATING

PLANE

C

TSSOP

DT SUFFIX

CASE 1201−01

ISSUE A

48X K REF

0.12 (0.005) M T U S

A

−V−

G

VS

25

24

J JÇÇÇÉÉÉ1 ÇÇÇÉÉÉKK1ÇÇÇÉÉÉ

SECTION N−N

B

−U−

N

NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI

Y14.5M, 1982.

2. CONTROLLING DIMENSION: MILLIMETER.

3. DIMENSIONS A AND B DO NOT INCLUDE

MOLD FLASH, PROTRUSIONS OR GATE

BURRS. MOLD FLASH OR GATE BURRS

SHALL NOT EXCEED 0.15 (0.006) PER SIDE.

4. DIMENSION K DOES NOT INCLUDE DAMBAR

PROTRUSION. ALLOWABLE DAMBAR

PROTRUSION SHALL BE 0.08 (0.003) TOTAL IN

EXCESS OF THE K DIMENSION AT MAXIMUM

MATERIAL CONDITION.

5. TERMINAL NUMBERS ARE SHOWN FOR

REFERENCE ONLY.

6. DIMENSIONS A AND B ARE TO BE

DETERMINED AT DATUM PLANE −W−.

N

FM

DETAIL E 0.25 (0.010)

DETAIL E

H

−W−

MILLIMETERS

INCHES

DIM MIN MAX MIN MAX

A 12.40 12.60 0.488 0.496

B 6.00 6.20 0.236 0.244

C −−− 1.10 −−− 0.043

D 0.05 0.15 0.002 0.006

F 0.50 0.75 0.020 0.030

G 0.50 BSC

0.0197 BSC

H 0.37 −−− 0.015 −−−

J 0.09 0.20 0.004 0.008

J1 0.09 0.16 0.004 0.006

K 0.17 0.27 0.007 0.011

K1 0.17 0.23 0.007 0.009

L 7.95 8.25 0.313 0.325

M 0_ 8_ 0_ 8_

ON Semiconductor and

are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice

to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability

arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.

“Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All

operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC does not convey any license under its patent rights

nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications

intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should

Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates,

and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death

associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal

Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

PUBLICATION ORDERING INFORMATION

LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor

P.O. Box 5163, Denver, Colorado 80217 USA

Phone: 303−675−2175 or 800−344−3860 Toll Free USA/Canada

Fax: 303−675−2176 or 800−344−3867 Toll Free USA/Canada

Email: [email protected]

N. American Technical Support: 800−282−9855 Toll Free

USA/Canada

Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910

Japan Customer Focus Center

Phone: 81−3−5773−3850

http://onsemi.com

11

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local

Sales Representative

74ALVC16374/D

11 Page | ||

| Páginas | Total 11 Páginas | |

| PDF Descargar | [ Datasheet 74ALVC16374.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| 74ALVC16373 | Low Voltage 16-Bit Transparent Latch with 3.6V Tolerant Inputs and Outputs | Fairchild Semiconductor |

| 74ALVC16373 | Low-Voltage 1.8/2.5/3.3V 16-Bit Transparent Latch | ON Semiconductor |

| 74ALVC16373GX | Low Voltage 16-Bit Transparent Latch with 3.6V Tolerant Inputs and Outputs | Fairchild Semiconductor |

| 74ALVC16373MTD | Low Voltage 16-Bit Transparent Latch with 3.6V Tolerant Inputs and Outputs | Fairchild Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |