|

|

PDF 74HC109 Data sheet ( Hoja de datos )

| Número de pieza | 74HC109 | |

| Descripción | Dual JK flip-flop with set and reset positive-edge trigger | |

| Fabricantes | Philips | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de 74HC109 (archivo pdf) en la parte inferior de esta página. Total 9 Páginas | ||

|

No Preview Available !

INTEGRATED CIRCUITS

DATA SHEET

For a complete data sheet, please also download:

• The IC06 74HC/HCT/HCU/HCMOS Logic Family Specifications

• The IC06 74HC/HCT/HCU/HCMOS Logic Package Information

• The IC06 74HC/HCT/HCU/HCMOS Logic Package Outlines

74HC/HCT109

Dual JK flip-flop with set and reset;

positive-edge trigger

Product specification

Supersedes data of December 1990

File under Integrated Circuits, IC06

1997 Nov 25

1 page

Philips Semiconductors

Dual JK flip-flop with set and reset;

positive-edge trigger

Product specification

74HC/HCT109

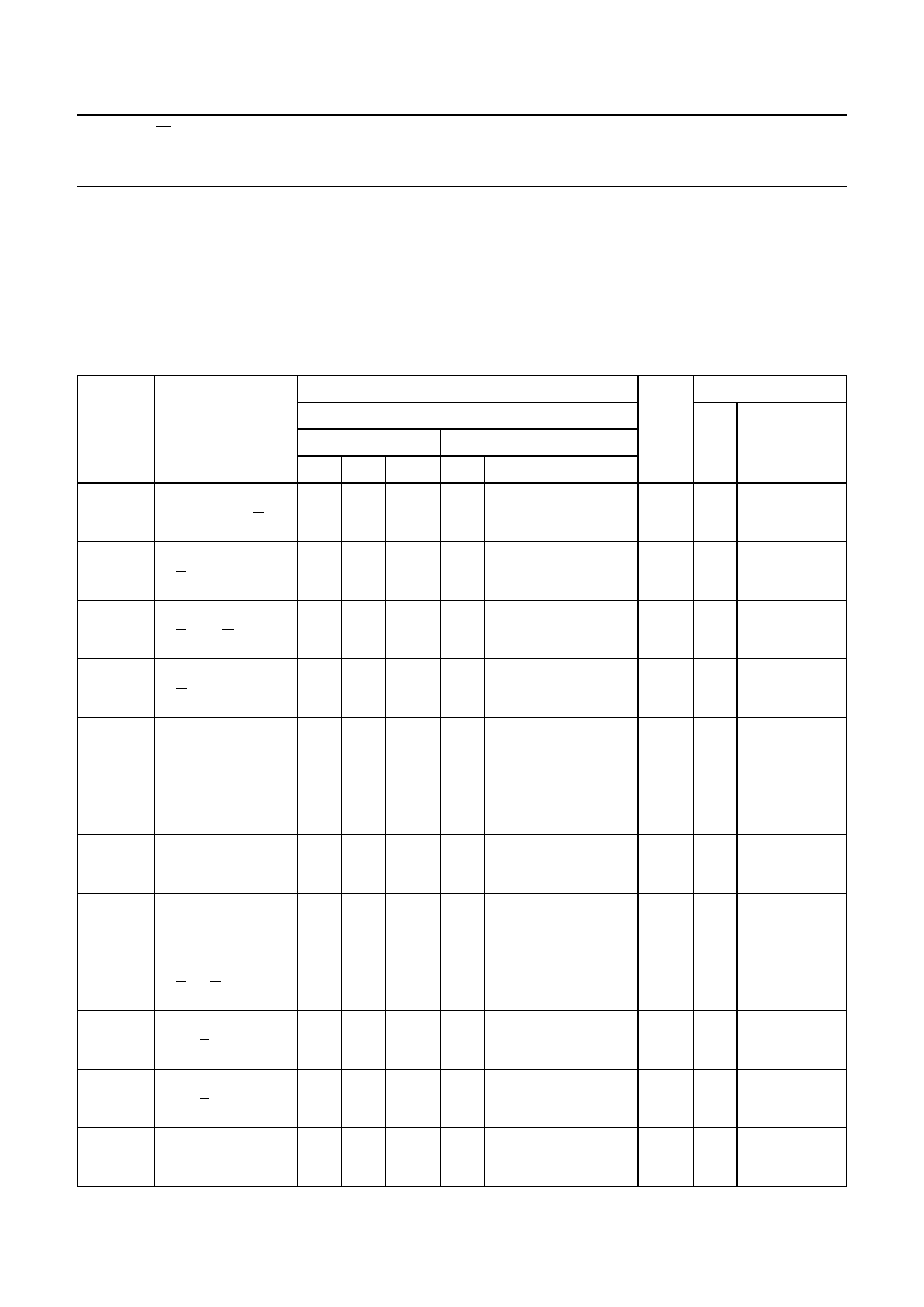

DC CHARACTERISTICS FOR 74HC

For the DC characteristics see “74HC/HCT/HCU/HCMOS Logic Family Specifications”.

Output capability: standard

ICC category: flip-flops

AC CHARACTERISTICS FOR 74HC

GND = 0 V; tr = tf = 6 ns; CL = 50 pF

Tamb (°C)

TEST CONDITIONS

SYMBOL

PARAMETER

+25

min. typ. max.

74HC

−40 to +85

min. max.

−40 to +125

min. max.

UNIT

VCC WAVEFORMS

(V)

tPHL/ tPLH

propagation delay

nCP to nQ, nQ

50 175

18 35

14 30

220

44

37

265

53 ns

45

2.0

4.5 Fig.6

6.0

tPLH

propagation delay

nSD to nQ

30 120

11 24

9 20

150

30

26

180

36 ns

31

2.0

4.5 Fig.7

6.0

tPHL

propagation delay

nSD to nQ

41 155

15 31

12 26

195

39

33

235

47 ns

40

2.0

4.5 Fig.7

6.0

tPHL

propagation delay

nRD to nQ

41 185

15 37

12 31

230

46

39

280

56 ns

48

2.0

4.5 Fig.7

6.0

tPLH

propagation delay

nRD to nQ

39 170

14 34

11 29

215

43

37

255

51 ns

43

2.0

4.5 Fig.7

6.0

tTHL/ tTLH

output transition

time

19 75

7 15

6 13

95

19

16

110

22 ns

19

2.0

4.5 Fig.6

6.0

tW

clock pulse width

HIGH or LOW

80 19

16 7

14 6

100 120

2.0

20 24 ns 4.5 Fig.6

17 20

6.0

tW

set or reset pulse

width HIGH or LOW

80

16

14

14

5

4

100 120

2.0

20 24 ns 4.5 Fig.7

17 20

6.0

trem

removal time

nSD, nRD to nCP

70

14

12

19

7

6

90

18

15

105 2.0

21 ns 4.5 Fig.7

18 6.0

tsu

set-up time

nJ, nK to nCP

70 17

14 6

12 5

90

18

15

105 2.0

21 ns 4.5 Fig.6

18 6.0

th

hold time

nJ, nK to nCP

50

50

50

5

5

5

5

5

5

2.0

ns 4.5 Fig.6

6.0

fmax

maximum clock

pulse frequency

6.0 22

30 68

35 81

5.0 4.0

2.0

24 20 MHz 4.5 Fig.6

28 24

6.0

1997 Nov 25

5

5 Page | ||

| Páginas | Total 9 Páginas | |

| PDF Descargar | [ Datasheet 74HC109.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| 74HC10 | Triple 3-input NAND gate | Philips |

| 74HC107 | Dual JK flip-flop with reset negative-edge trigger | Philips |

| 74HC109 | Dual JK flip-flop with set and reset positive-edge trigger | Philips |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |