|

|

PDF 74AHC374PW Data sheet ( Hoja de datos )

| Número de pieza | 74AHC374PW | |

| Descripción | Octal D-type flip-flop; positive edge-trigger; 3-state | |

| Fabricantes | NXP Semiconductors | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de 74AHC374PW (archivo pdf) en la parte inferior de esta página. Total 20 Páginas | ||

|

No Preview Available !

INTEGRATED CIRCUITS

DATA SHEET

74AHC374; 74AHCT374

Octal D-type flip-flop; positive

edge-trigger; 3-state

Product specification

Supersedes data of 1998 Dec 11

File under Integrated Circuits, IC06

1999 Sep 28

1 page

Philips Semiconductors

Octal D-type flip-flop; positive edge-trigger; 3-state

Product specification

74AHC374;

74AHCT374

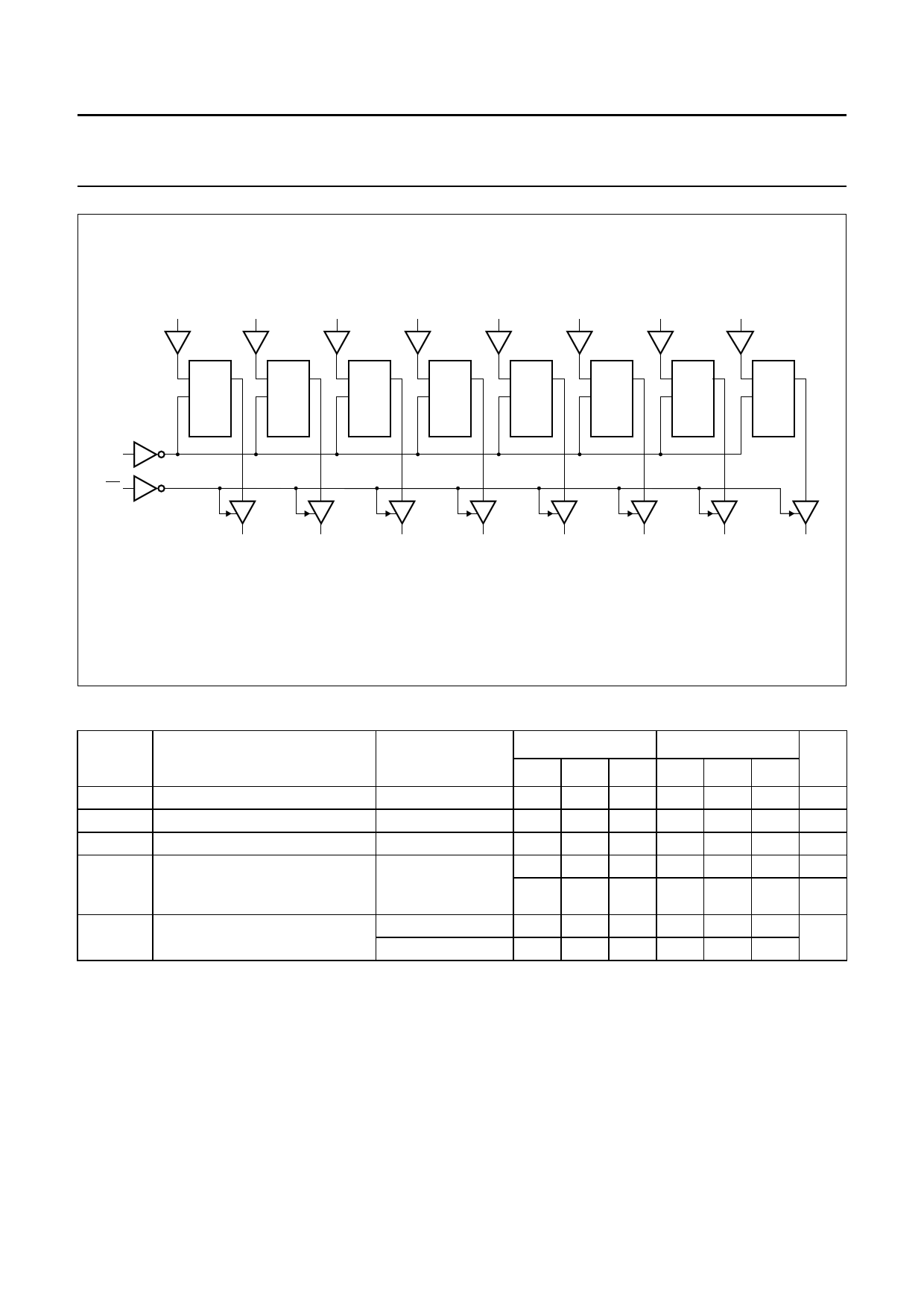

D0 D1 D2 D3 D4 D5 D6 D7

DQ

CP

FF1

DQ

CP

FF2

DQ

CP

FF3

DQ

CP

FF4

DQ

CP

FF5

DQ

CP

FF6

DQ

CP

FF7

DQ

CP

FF8

CP

OE

Q0 Q1 Q2 Q3 Q4 Q5 Q6 Q7

MNA198

Fig.5 Logic diagram.

RECOMMENDED OPERATING CONDITIONS

SYMBOL

PARAMETER

VCC

VI

VO

Tamb

DC supply voltage

input voltage

output voltage

operating ambient temperature

range

tr,tf (∆t/∆f) input rise and fall rates

CONDITIONS

74AHC

74AHCT

UNIT

MIN. TYP. MAX. MIN. TYP. MAX.

2.0 5.0 5.5 4.5 5.0 5.5 V

0 − 5.5 0 − 5.5 V

0 − VCC 0 − VCC V

see DC and AC −40 +25 +85 −40 +25 +85 °C

characteristics per −40 +25 +125 −40 +25 +125 °C

device

VCC = 3.3 V ±0.3 V − − 100 − − − ns/V

VCC = 5 V ±0.5 V − − 20 − − 20

1999 Sep 28

5

5 Page

Philips Semiconductors

Octal D-type flip-flop; positive edge-trigger; 3-state

Product specification

74AHC374;

74AHCT374

Type 74AHCT374

GND = 0 V; tr = tf ≤ 3.0 ns.

SYMBOL PARAMETER

TEST CONDITIONS

WAVEFORMS CL

Tamb (°C)

25 −40 to +85 −40 to +125 UNIT

MIN. TYP. MAX. MIN. MAX. MIN. MAX.

VCC = 4.5 to 5.5 V; note 1

tPHL/tPLH propagation delay see Figs 6, 8

CP to Qn

and 9

15 pF −

4.3 9.4 1.0 10.5 1.0 12.0 ns

tPZH/tPZL propagation delay see Figs 7 and 9

OE to Qn

− 3.5 10.2 1.0 11.5 1.0 13.0 ns

tPHZ/tPLZ propagation delay

OE to Qn

− 3.6 10.2 1.0 11.0 1.0 13.0 ns

fmax maximum clock see Figs 6 and 9

pulse frequency

90 140 −

80 −

80 −

MHz

tPHL/tPLH

tPZH/tPZL

tPHZ/tPLZ

tW

propagation delay

CP to Qn

propagation delay

OE to Qn

propagation delay

OE to Qn

clock pulse width

HIGH or LOW

see Figs 6, 8

and 9

see Figs 7 and 9

see Figs 6 and 9

50 pF

−

−

−

6.5

5.6

4.8

5.7

−

10.4 1.0 11.5 1.0 13.0 ns

11.2 1.0 12.5 1.0 14.0 ns

11.2 1.0 12.0 1.0 14.0 ns

− 6.5 − 6.5 − ns

tsu set-up time see Figs 8 and 9

Dn to CP

th hold time

Dn to CP

fmax maximum clock see Figs 6 and 9

pulse frequency

2.5 −

−

2.5 −

−

85 130 −

2.5 −

2.5 −

75 −

2.5 −

2.5 −

75 −

ns

ns

MHz

Note

1. Typical values at VCC = 5.0 V.

1999 Sep 28

11

11 Page | ||

| Páginas | Total 20 Páginas | |

| PDF Descargar | [ Datasheet 74AHC374PW.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| 74AHC374PW | Octal D-type flip-flop; positive edge-trigger; 3-state | NXP Semiconductors |

| 74AHC374PWDH | Octal D-type flip-flop; positive edge-trigger; 3-state | NXP Semiconductors |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |