|

|

PDF 5821 Data sheet ( Hoja de datos )

| Número de pieza | 5821 | |

| Descripción | BiMOS II 8-Bit Serial Input Latched Driver | |

| Fabricantes | Allegro MicroSystems | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de 5821 (archivo pdf) en la parte inferior de esta página. Total 8 Páginas | ||

|

No Preview Available !

A5821

BiMOS II 8-Bit Serial Input Latched Driver

Discontinued Product

These parts are no longer in production The device should not be

purchased for new design applications. Samples are no longer available.

Date of status change: October 31, 2005

Recommended Substitutions:

For new customers or new applications, refer to the A6821.

NOTE: For detailed information on purchasing options, contact your

local Allegro field applications engineer or sales representative.

Allegro MicroSystems, Inc. reserves the right to make, from time to time, revisions to the anticipated product life cycle plan for a

product to accommodate changes in production capabilities, alternative product availabilities, or market demand. The information

included herein is believed to be accurate and reliable. However, Allegro MicroSystems, Inc. assumes no responsibility for its use; nor

for any infringements of patents or other rights of third parties which may result from its use.

1 page

5821

8-BIT SERIAL-INPUT,

LATCHED DRIVERS

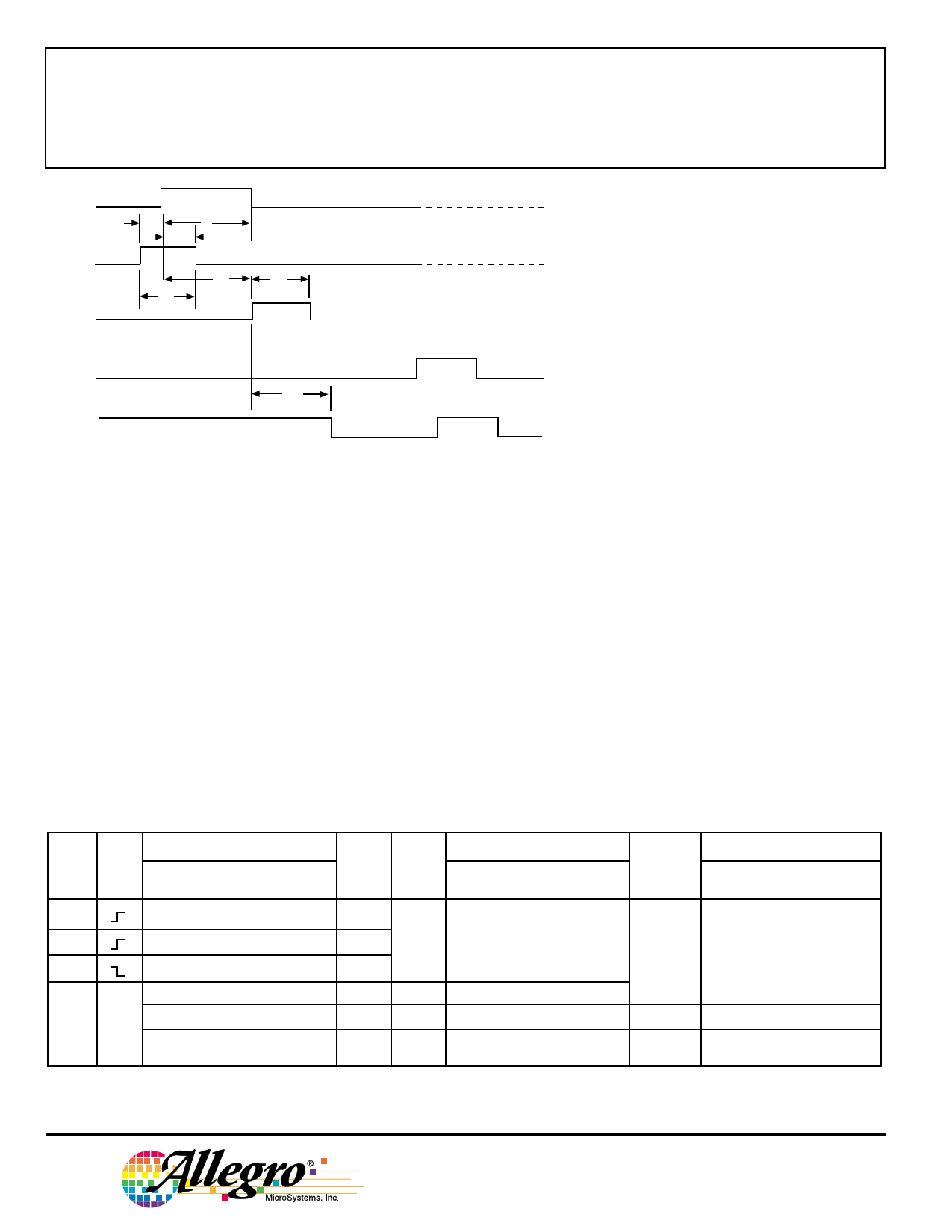

CLOCK

DATA IN

STROBE

AD

B

E

C

F

OUTPUT

ENABLE

OUTN

G

Dwg. No. A-12,627

TIMING CONDITIONS

(VDD = 5.0 V, TA = +25°C, Logic Levels are VDD and Ground)

A. Minimum Data Active Time Before Clock Pulse

(Data Set-Up Time) ....................................................................... 75 ns

B. Minimum Data Active Time After Clock Pulse

(Data Hold Time) ........................................................................... 75 ns

C. Minimum Data Pulse Width .............................................................. 150 ns

D. Minimum Clock Pulse Width ............................................................ 150 ns

E. Minimum Time Between Clock Activation and Strobe ....................... 30 ns

F. Minimum Strobe Pulse Width ........................................................... 100 ns

G. Typical Time Between Strobe Activation and

Output Transition .......................................................................... 1.0 µs

Serial Data present at the input is

transferred to the shift register on the

logic “0” to logic “1” transition of the

CLOCK input pulse. On succeeding

CLOCK pulses, the registers shift data

information towards the SERIAL DATA

OUTPUT. The SERIAL DATA must

appear at the input prior to the rising edge

of the CLOCK input waveform.

Information present at any register is

transferred to its respective latch when the

STROBE is high (serial-to-parallel con-

version). The latches will continue to

accept new data as long as the STROBE

is held high. Applications where the

latches are bypassed (STROBE tied high)

will require that the ENABLE input be

high during serial data entry.

When the ENABLE input is high, all

of the output buffers are disabled (OFF)

without affecting the information stored

in the latches or shift register. With the

ENABLE input low, the outputs are

controlled by the state of the latches.

Serial

Shift Register Contents

Data Clock

Input Input I1 I2 I3 .............. I8

TRUTH TABLE

Serial

Latch Contents

Data Strobe

Output Input I1 I2 I3 .............. I8

Output

Enable

Output Contents

I1 I2 I3 .............. I8

H

H R1 R2 .............. R7

R7

L

L R1 R2 .............. R7

R7

X

R1 R2 R3 .............. R8

R8

X X X .............. X

X

L R1 R2 R3 .............. R8

P1 P2 P3 .............. P8

P8

H P1 P2 P3 .............. P8

L

P1 P2 P3 .............. P8

X X X .............. X

H H H H .............. H

L = Low Logic Level H = High Logic Level X = Irrelevant P = Present State R = Previous State

115 Northeast Cutoff, Box 15036

Worcester, Massachusetts 01615-0036 (508) 853-5000

5 Page | ||

| Páginas | Total 8 Páginas | |

| PDF Descargar | [ Datasheet 5821.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| 5821 | BiMOS II 8-Bit Serial Input Latched Driver | Allegro MicroSystems |

| 5822 | BiMOS II 8-Bit Serial Input Latched Driver | Allegro MicroSystems |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |