|

|

PDF 74ALVC244BQ Data sheet ( Hoja de datos )

| Número de pieza | 74ALVC244BQ | |

| Descripción | Octal buffer/line driver; 3-state | |

| Fabricantes | NXP Semiconductors | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de 74ALVC244BQ (archivo pdf) en la parte inferior de esta página. Total 15 Páginas | ||

|

No Preview Available !

INTEGRATED CIRCUITS

DATA SHEET

74ALVC244

Octal buffer/line driver; 3-state

Product specification

Supersedes data of 2003 Aug 11

2003 Sep 08

1 page

Philips Semiconductors

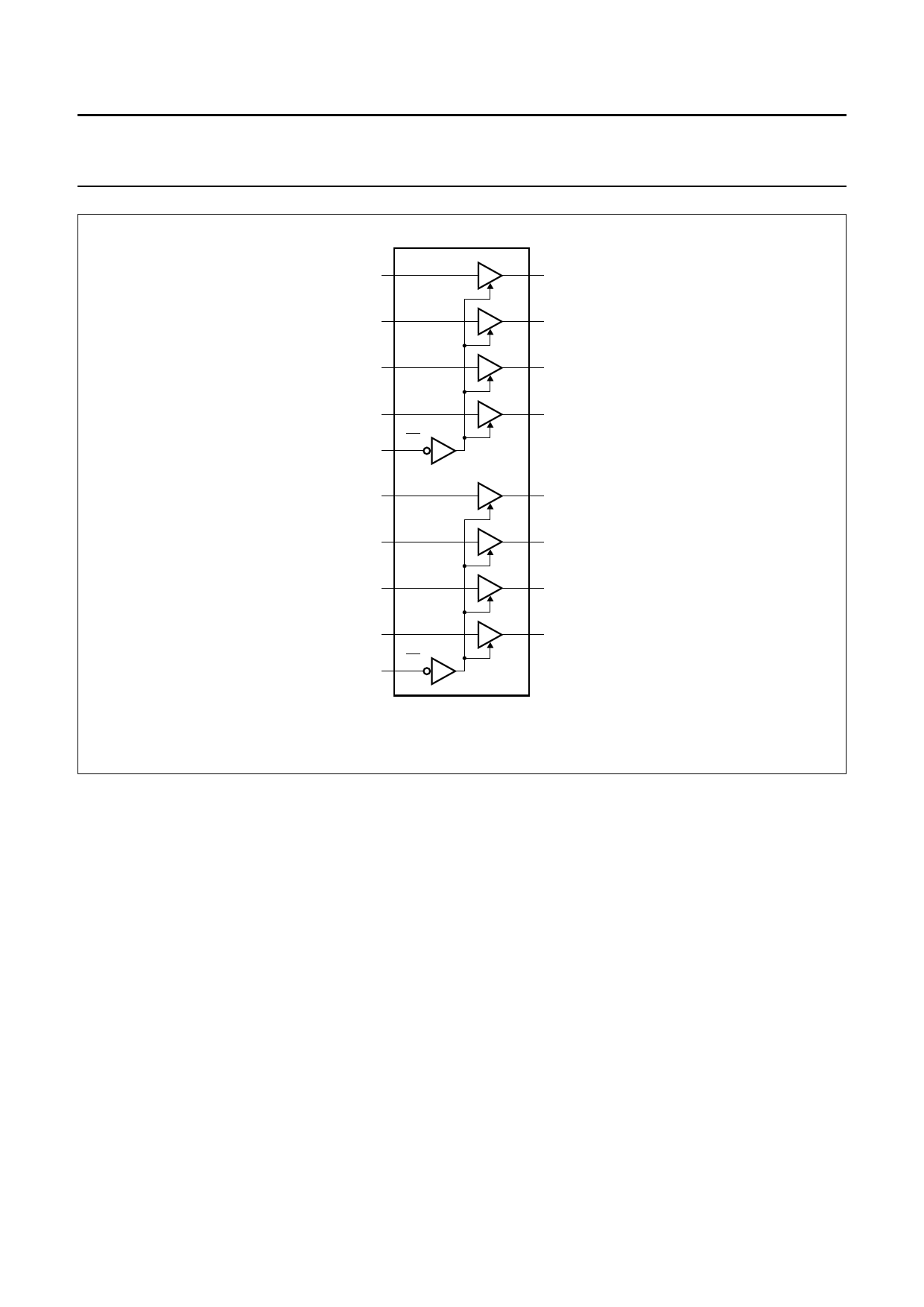

Octal buffer/line driver; 3-state

handbook, halfpage

2

1A0

1A1

4

1A2

6

1A3

8

1OE

1

2A0

17

2A1

15

2A2

13

2A3

11

2OE

19

1Y0

18

1Y1

16

1Y2

14

1Y3

12

2Y0

3

2Y1

5

2Y2

7

2Y3

9

MNA170

Fig.5 Logic diagram.

Product specification

74ALVC244

2003 Sep 08

5

5 Page

Philips Semiconductors

Octal buffer/line driver; 3-state

PACKAGE OUTLINES

SO20: plastic small outline package; 20 leads; body width 7.5 mm

Product specification

74ALVC244

SOT163-1

y

Z

20

D

c

11

EA

X

HE v M A

pin 1 index

1

e

10

wM

bp

A2

A1

Q

(A 3)

A

Lp

L

detail X

θ

0 5 10 mm

scale

DIMENSIONS (inch dimensions are derived from the original mm dimensions)

A

UNIT max. A1 A2 A3 bp

c

D (1) E (1)

e

HE

L

Lp

Q

v

mm

2.65

0.3

0.1

2.45

2.25

0.25

0.49

0.36

0.32

0.23

13.0

12.6

7.6

7.4

1.27

10.65

10.00

1.4

1.1

0.4

1.1

1.0

0.25

inches

0.1

0.012 0.096

0.004 0.089

0.01

0.019 0.013

0.014 0.009

0.51

0.49

0.30

0.29

0.05

0.419

0.394

0.055

0.043

0.016

0.043

0.039

0.01

w y Z (1)

0.25

0.01

0.1

0.9

0.4

0.004

0.035

0.016

θ

8o

0o

Note

1. Plastic or metal protrusions of 0.15 mm (0.006 inch) maximum per side are not included.

OUTLINE

VERSION

SOT163-1

IEC

075E04

REFERENCES

JEDEC

JEITA

MS-013

EUROPEAN

PROJECTION

ISSUE DATE

99-12-27

03-02-19

2003 Sep 08

11

11 Page | ||

| Páginas | Total 15 Páginas | |

| PDF Descargar | [ Datasheet 74ALVC244BQ.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| 74ALVC244BQ | Octal buffer/line driver; 3-state | NXP Semiconductors |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |