|

|

PDF AP0202AT Data sheet ( Hoja de datos )

| Número de pieza | AP0202AT | |

| Descripción | High-Dynamic Range (HDR) Image Signal Processor | |

| Fabricantes | ON Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de AP0202AT (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

‡Advance

AP0202AT: Image Signal Processor (ISP)

Features

AP0202AT High-Dynamic Range (HDR) Image

Signal Processor (ISP)

AP0202AT Datasheet, Rev. 4

For the latest product datasheet, please visit www.onsemi.com

Features

• Up to 2.0 Mp (1920x1080) ON Semiconductor sensor

support

• 30 fps at 1080p, 45 fps at 1.2Mp, 60 fps at 720p

(Optimized for operation with HDR sensors)

• Color and gamma correction

• Auto exposure, auto white balance, 50/60 Hz auto

flicker detection and avoidance

• Adaptive Local Tone Mapping (ALTM)

• Two-wire serial programming interface (CCIS)

• Parallel output

• Configurable through low-cost SPI Flash and

EEPROM devices

• High-level host command interface

• Standalone operation supported

• Up to 7 GPIO

• Fail-safe IO

• Multi-Camera synchronization support

Applications

• Surround, rear and front view cameras

• Blind spot / side mirror replacement cameras

• Automotive viewing/processing fusion cameras

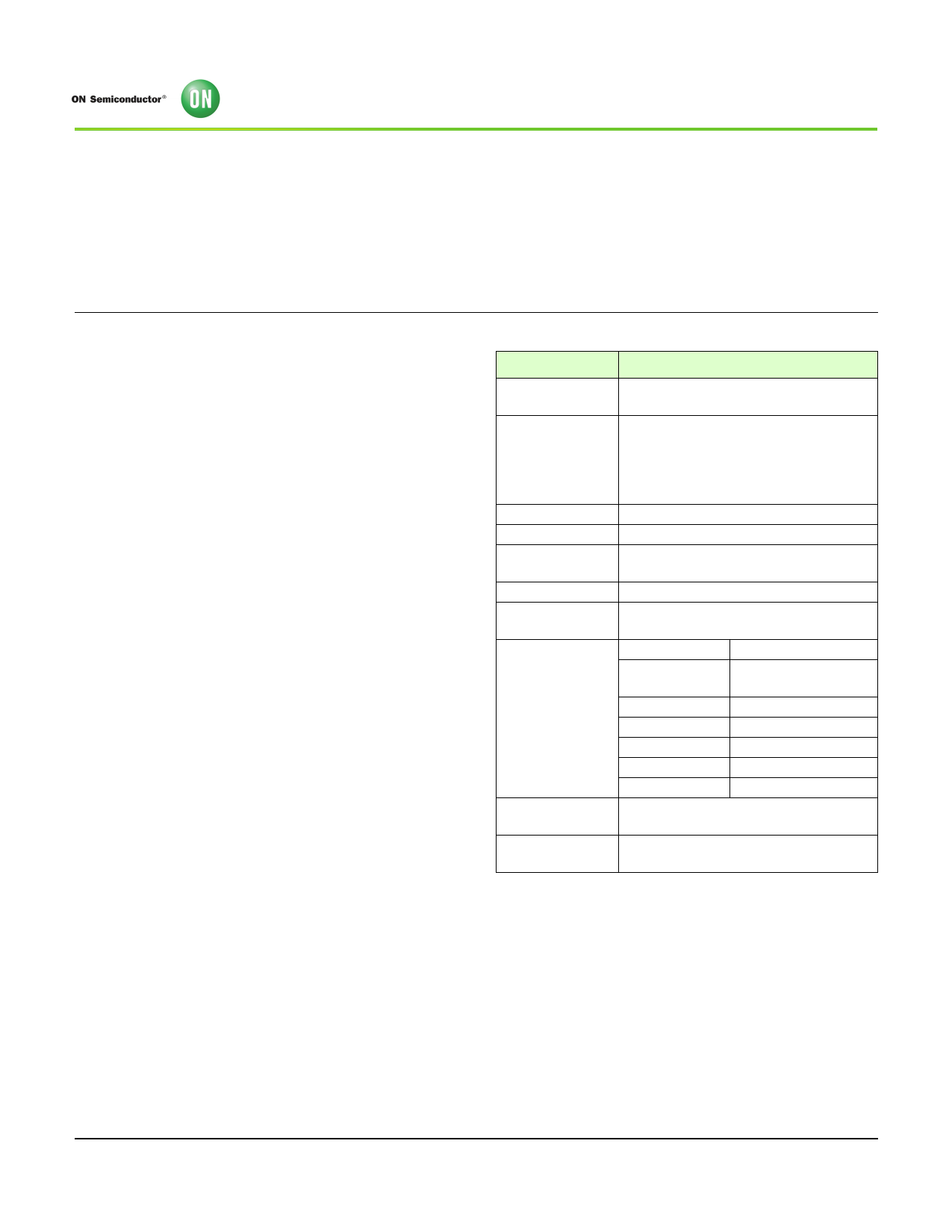

Table 1:

Key Performance Parameters

Parameter

Image sensor

interfaces

Input Data

FOrmat

Value

Parallel and HiSPi

Parallel: 12 bit SDR (linear) or

12 bit HDR companded.

Output interface

Output format

Maximum

resolution

Input clock range

Output pixel clock

maximum

Supply voltage

Operating temp.

(Ambient)

Power

consumption

HiSPI: 12 bit SDR (linear) or

12/14 bit HDR companded

Up to 24-bit parallel1

RGB888, RGB565, YUV422 8-/10-bit1

1920 x 1080 (2.0 Mp)

10 - 29 MHz

125 MHz2

VDDIO_S

VDDIO_H

VDD_REG

VDD

VDD_PLL

VDD_PHY

VDDIO_OTPM

–40°C to +105°C

1.8 or 2.8 V nominal

1.8 or 2.8 or 3.3 V

nominal

1.8 V nominal

1.2 V nominal

1.2 V nominal

2.8 V nominal

2.5 to 3.3 V nominal

250 mW

Notes: 1. Maximum frame rates depend on output interface and

data format configuration used.

2. Maximum pixel clock rates depend on IO voltage.

AP0202AT/D Rev. 4, 9/15 EN

1 ©Semiconductor Components Industries, LLC 2015,

‡This document contains information on a new product. Specifications and information herein are subject to change without notice.

1 page

Advance

AP0202AT: Image Signal Processor (ISP)

List of Tables

List of Tables

Table 1:

Table 2:

Table 3:

Table 4:

Table 5:

Table 6:

Table 7:

Table 8:

Table 9:

Table 10:

Table 11:

Table 12:

Table 13:

Table 14:

Table 15:

Table 16:

Table 17:

Table 18:

Table 19:

Table 20:

Table 21:

Table 22:

Table 23:

Table 24:

Table 25:

Table 26:

Table 27:

Table 28:

Table 29:

Table 30:

Table 31:

Table 32:

Table 33:

Table 34:

Table 35:

Key Performance Parameters. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1

Available Part Numbers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2

Pin Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11

Package Pinout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12

Key Signals When Using the Regulator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13

Power-Up and Power-Down Signal Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13

Output States . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15

Hard Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17

Hard Standby Signal Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18

YCbCr Output Data Ordering. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .26

YCbCr Output Modes (Default mode; cam_port_parallel_msb_align=0x1) . . . . . . . . . . . . . . . . . . . . .26

YCbCr Output Modes (Default mode; cam_port_parallel_msb_align=0x0) . . . . . . . . . . . . . . . . . . . . .27

RGB888 Output Modes (cam_port_parallel_msb_align=0x01) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .32

RGB888 Output Modes (cam_port_parallel_msb_align=0x0). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .32

RGB565Output Modes (cam_port_parallel_msb_align=0x01) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .35

RGB565 Output Modes (cam_port_parallel_msb_align=0x0). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .35

ALTM Bayer Output Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .37

12-bit Bayer Output Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .37

14-bit Bayer Output Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .37

16-bit Bayer Output Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .37

20-bit Bayer Output Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .37

Two-Wire Interface ID Address Switching . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .39

Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .44

Electrical Characteristics and Operating Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .44

I/O Timing Characteristics - Parallel Mode (2.8V VDD_IO)1.2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .45

I/O Timing Characteristics - Parallel Mode (1.8V VDD_IO)1.2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .46

DC Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .46

Input Clocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .46

Output Clocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .47

Trigger Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .48

Standby Current Consumption . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .48

Inrush Current. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .48

Operating Current Consumption . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .49

Slave Two-Wire Serial Bus Characteristics (CCIS) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .50

Master Two-Wire Serial Bus Characteristics (CCIM) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .51

AP0202AT/D Rev. 4, Pub. 9/15 EN

5 ©Semiconductor Components Industries, LLC, 2015.

5 Page

Advance

AP0202AT: Image Signal Processor (ISP)

System Interfaces

Pin Descriptions

Table 3:

Pin Descriptions

Name

EXTCLK

XTAL

RESET_BAR

SCLK

SDATA

SADDR

FRAME_SYNC

STANDBY

EXT_REG

ENDLO

SPI_SCLK

SPI_SDI

SPI_SDO

SPI_CS_BAR

EXT_CLK_OUT

RESET_BAR_OUT

M_SCLK

M_SDATA

FV_IN

LV_IN

PIXCLK_IN

DIN[11:0]

HiSPiCN

HiSPiCP

HiSPi0N

HiSPi0P

HiSPi1N

HiSPi1P

TRIGGER_OUT/GPIO_0

FV_OUT

META_LINE_VALID

LV_OUT

PIXCLK_OUT

DOUT[23:0]

Type

Input

Output

Input/PU

Input

I/O

Input

Input

Input

Input

Input

Output

Input

Output

Output

Output

Output

Output

I/O

Input

Input

Input

Input

Input

Input

Input

Input

Input

Input

Output

Output

Output

Output

Output

Output

Description

Master input clock. This can either be a square-wave generated from an

oscillator (in which case the XTAL input must be left unconnected) or direct

connection to a crystal.

If EXTCLK is connected to one pin of a crystal, the other pin of the crystal is

connected to XTAL pin; otherwise this signal must be left unconnected.

Master reset signal, active LOW. This signal has an internal pull up.

Two-wire serial interface clock (host interface).

Two-wire serial interface data (host interface).

Selects device address for the two-wire slave serial interface. When connected

to GND the device ID is 0x90. When wired to VDDIO_H, a device ID of 0xBA is

selected.

Pass through to TRIGGER_OUT. This signal should be connected to GND if not

used.

Standby mode control, active HIGH.

Select external regulator if tied high

Regulator enable (VDD_REG domain)

Clock output for interfacing to an external SPI flash or EEPROM memory.

Data in from SPI flash or EEPROM memory. When no SPI device is fitted, this

signal is used to determine whether the AP0202AT should auto-configure:

0: Do not auto-configure; Two-wire interface will be used to configure the

device (host-config mode)

1: Auto-configure. This signal has an internal pull-up resistor.

Data out to SPI flash or EEPROM memory.

Chip select out to SPI flash or EEPROM memory.

Clock to external sensor.

Reset signal to external signal.

Two-wire serial interface clock (Master).

Two-wire serial interface clock (Master).

Sensor frame valid input.

Sensor line valid input.

Sensor pixel clock input.

Sensor pixel data input DIN[11:0]

Differential HiSPi clock (negative).

Differential HiSPi clock (positive).

Differential HiSPi data, lane 0 (negative).

Differential HiSPi data, lane 0 (positive).

Differential HiSPi data, lane 1 (negative).

Differential HiSPi data, lane 1 (positive).

Trigger signal for external sensor.

Host frame valid output (synchronous to PIXCLK_OUT)

Line valid signal to indicate when Metadata is valid. In addition, there is a

variable option to allow META_LINE_VALID to be reflected in LV_OUT

Host line valid output (synchronous to PIXCLK_OUT)

Host pixel clock output.

Host pixel data output (synchronous to H_PIXCLK_OUT) .

AP0202AT/D Rev. 4, Pub. 9/15 EN

11

©Semiconductor Components Industries, LLC, 2015.

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet AP0202AT.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| AP0202AT | High-Dynamic Range (HDR) Image Signal Processor | ON Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |