|

|

PDF GM0936TQ Data sheet ( Hoja de datos )

| Número de pieza | GM0936TQ | |

| Descripción | Voice-Band Audio CODEC for CDMA | |

| Fabricantes | Hynix Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de GM0936TQ (archivo pdf) en la parte inferior de esta página. Total 21 Páginas | ||

|

No Preview Available !

GM0936TQ

GM0936TQ

Voice-Band Audio CODEC for CDMA

Features

• Single 3-V operation

• Low power consumption

– Operating mode .... 20mW Typ

– Power-down mode ... 1mW Typ

• Combined A/D, D/A, and Filters

• Electret microphone bias reference

voltage available

• Compatible with all digital signal

processors (DSPs)

• Programmable volume control

• 300 Hz - 3.6 kHz Passband with Specified

Master clock

20 DIP/SOP

(TOP VIEW)

• Designed for standard 2.048MHz master

clock for U.S. Analog, U.S. Digital, CT2,

DECT, GSM, and PCS Standards for

Hand-held Battery-Powered Telephones

• On-chip voltage references

• Package Type : 48 LQFP, 20 DIP, 20 SOP

48 LQFP

(TOP VIEW)

____

PDN

EARA

EARB

EARGS

_______V__c_c

MICMUTE

NC

DIN

_______F_S_R_

EARMUTE

1

2

3

4

5

6

7

8

9

10

20 MICBIAS

19 MICGS

18 MICIN

17 VMID

16 GND

15 NC

14 NC

13 DOUT

12 FSX

11 CLK

NC

NC

NC

AVcc

NC

NC

NC

NC

DVcc

_______N__C_

MICMUTE

NC

1

2

3

4

5

6

7

8

9

10

11

12

36 VMID

35 NC

34 AGND

33 NC

32 NC

31 NC

30 NC

29 NC

28 NC

27 DGND

26 NC

25 NC

1

1 page

GM0936TQ

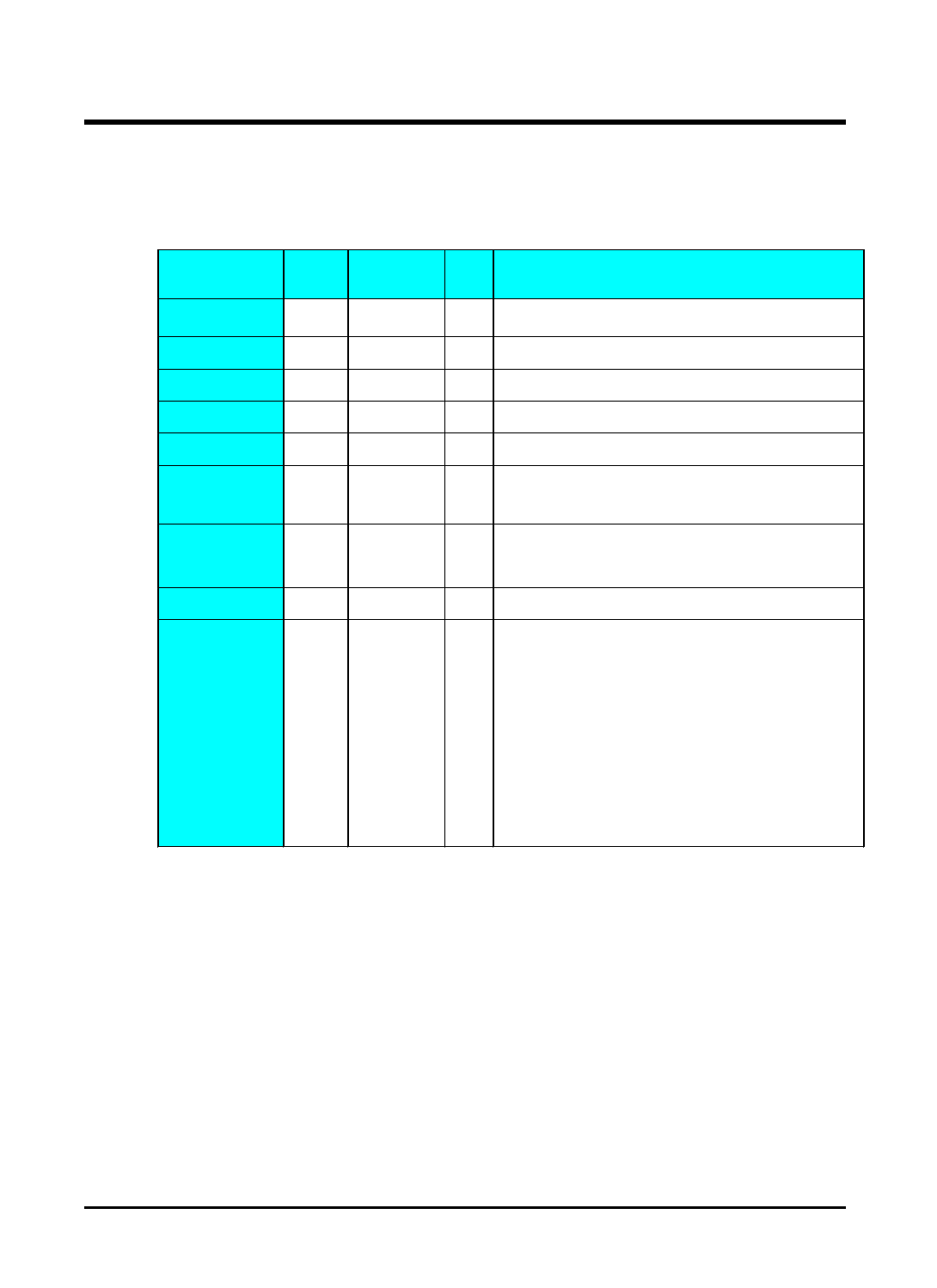

Pin Description

DIGITAL SIGNALS

TERMINAL

NAME

CLK

DGND

DIN

DOUT

DVcc

FSR

FSX

PDN_

NC

LQFP SOP&DIP I/O DESCRIPTION

19 11

27 16

15 8

21 13

95

16 9

I Clock input (2.048 MHz)

Digital ground

I Receive data input

O Transmit data output

Digital power (3 V)

I

Frame-synchronization clock input for

receive channel

20 12

I

43

1,2,3,

5,6,7,

8,10,

12,13,

14,18,

22,23,

24,25,

26,28,

29,30,

31,32,

33,35

1

7, 14, 15

I

Frame-synchronization clock input for

receive channel

Power-down input, Active Low

No internal connection

5

5 Page

GM0936TQ

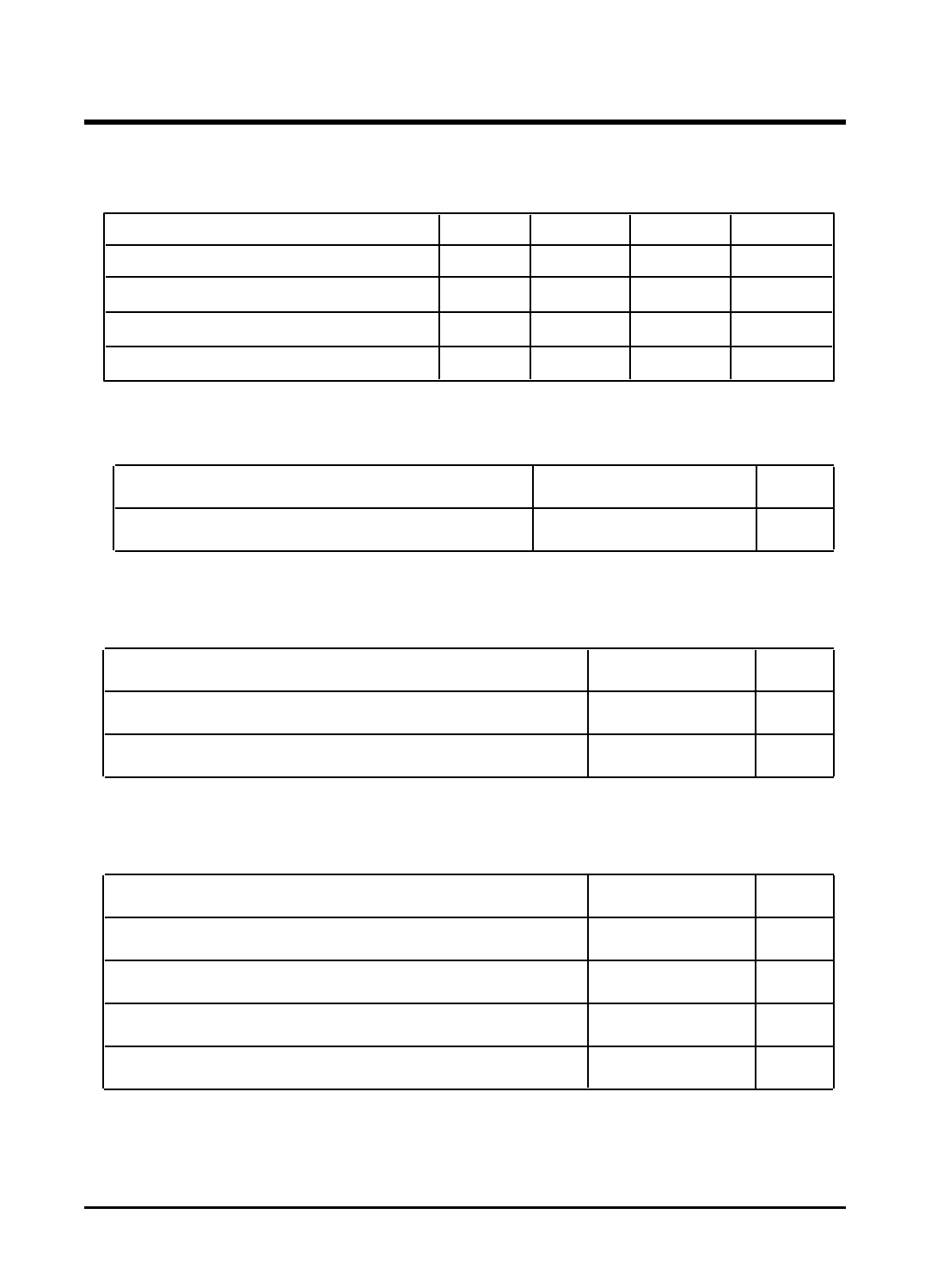

Timing (TA=25¡ É, DVCC = AVCC = 3V)

PARAMETER

CLK Frequency

Sampling Rate

DOUT Delay from CLK

DIN Delay from CLK

MIN

TYP

2.048

8

MAX

35

35

UNIT

MHz

KHz

ns

ns

Clock timing requirements

Duty cycle, CLK

MIN NOM MAX

45% 50% 55%

UNIT

Transmit timing requirements

tsu(FSX)

th(FSX)

Setup time, FSX high before CLK ¡ é

Hold time, FSX high after CLK ¡ é

Receive timing requirements

tsu(FSR)

th(FSR)

tsu(DIN)

th(DIN)

Setup time, FSR high before CLK ¡ é

Hold time, FSR high after CLK ¡ é

Setup time, DIN high or low before CLK ¡ é

Hold time, DIN high or low after CLK ¡ é

MIN MAX

20 468

20 468

UNIT

ns

ns

MIN MAX

20 468

20 468

20

20

UNIT

ns

ns

ns

ns

11

11 Page | ||

| Páginas | Total 21 Páginas | |

| PDF Descargar | [ Datasheet GM0936TQ.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| GM0936TQ | Voice-Band Audio CODEC for CDMA | Hynix Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |