|

|

PDF AT45DB321D Data sheet ( Hoja de datos )

| Número de pieza | AT45DB321D | |

| Descripción | 2.5V or 2.7V DataFlash | |

| Fabricantes | Adesto | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de AT45DB321D (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

AT45DB321D

32Mb, 2.5V or 2.7V

DataFlash

DATASHEET

(NOT RECOMMENDED FOR NEW DESIGNS. USE AT45DB321E.)

Features

● Single 2.5V - 3.6V or 2.7V - 3.6V supply

● RapidS™ serial interface: 66MHz maximum clock frequency

● SPI compatible modes 0 and 3

● User configurable page size

● 512 bytes per page

● 528 bytes per page

● Page size can be factory preconfigured for 512 bytes

● Page program operation

● Intelligent programming operation

● 8,192 pages (512/528 bytes/page) main memory

● Flexible erase options

● Page erase (512 bytes)

● Block erase (4KB)

● Sector erase (64KB)

● Chip erase (32Mb)

● Two SRAM data buffers (512/528 bytes)

● Allows receiving data while reprogramming the flash array

● Continuous read capability through entire array

● Ideal for code shadowing applications

● Low power dissipation

● 7mA active read current ,typical

● 25μA standby current, typical

● 15μA deep power down, typical

● Hardware and software data protection features

● Individual sector

● Sector lockdown for secure code and data storage

● Individual sector

● Security: 128-byte security register

● 64-byte user programmable space

● Unique 64-byte device identifier

● JEDEC standard manufacturer and device ID read

● 100,000 program/erase cycles per page, minimum

● Data retention: 20 years

● Industrial temperature range

● Green (Pb/halide-free/RoHS compliant) packaging options

3597T–DFLASH–11/2013

1 page

3. Device Operation

The device operation is controlled by instructions from the host processor. The list of instructions and their associated opcodes

are contained in Table 13-1 on page 24 through Table 13-7 on page 27. A valid instruction starts with the falling edge of CS,

followed by the appropriate 8-bit opcode and the desired buffer or main memory address location. While the CS pin is low,

toggling the SCK pin controls the loading of the opcode and the desired buffer or main memory address location through the SI

(serial input) pin. All instructions, addresses, and data are transferred with the most-significant bit (msb) first.

Buffer addressing for the standard DataFlash page size (528 bytes) is referenced in the datasheet using the terminology BFA9

- BFA0 to denote the ten address bits required to designate a byte address within a buffer. Main memory addressing is

referenced using the terminology PA12 - PA0 and BA9 - BA0, where PA12 - PA0 denotes the 13 address bits required to

designate a page address and BA9 - BA0 denotes the ten address bits required to designate a byte address within the page.

For a “power of two” binary page size (512 bytes), the buffer addressing is referenced in the datasheet using the conventional

terminology BFA8 - BFA0 to denote the nine address bits required to designate a byte address within a buffer. Main memory

addressing is referenced using the terminology A21 - A0, where A21 - A9 denotes the 13 address bits required to designate a

page address and A8 - A0 denotes the nine address bits required to designate a byte address within a page.

4. Read Commands

By specifying the appropriate opcode, data can be read from the main memory or from either one of the two SRAM data buffers.

The DataFlash device supports RapidS protocols for Mode 0 and Mode 3. Please refer to Section 22., Detailed Bit-level Read

Waveform – RapidS Serial Interface Mode 0/Mode 3 diagrams in this datasheet for details on the clock cycle sequences for

each mode.

4.1 Continuous Array Read (Legacy Command: E8H): Up to 66MHz

By supplying an initial starting address for the main memory array, the continuous array read command can be utilized to

sequentially read a continuous stream of data from the device by simply providing a clock signal; no additional addressing

information or control signals need to be provided. The DataFlash device incorporates an internal address counter that will

automatically increment on every clock cycle, allowing one continuous read operation without the need of additional address

sequences. To perform a continuous read from the standard DataFlash page size (528 bytes), an opcode of E8H must be

clocked into the device, followed by three address bytes (which comprise the 24-bit page and byte address sequence) and four

“don’t care” bytes. The first 13 bits (PA12 - PA0) of the 23-bit address sequence specify which page of the main memory array

to read, and the last 10 bits (BA9 - BA0) of the 23-bit address sequence specify the starting byte address within the page. To

perform a continuous read from the binary page size (512-bytes), the opcode (E8H) must be clocked into the device followed by

three address bytes and four don’t care bytes. The first 13 bits (A21 - A9) of the 22-bit sequence specify which page of the main

memory array to read, and the last 9 bits (A8 - A0) of the 22-bit address sequence specify the starting byte address within the

page. The don’t care bytes that follow the address bytes are needed to initialize the read operation. Following the don’t care

bytes, additional clock pulses on the SCK pin will result in data being output on the SO (serial output) pin.

The CS pin must remain low during the loading of the opcode, the address bytes, the don’t care bytes, and the reading of data.

When the end of a page in main memory is reached during a continuous array read, the device will continue reading at the

beginning of the next page, with no delays incurred during the page boundary crossover (the crossover from the end of one

page to the beginning of the next page). When the last bit in the main memory array has been read, the device will continue

reading back at the beginning of the first page of memory. As with crossing over page boundaries, no delays will be incurred

when wrapping around from the end of the array to the beginning of the array.

A low-to-high transition on the CS pin will terminate the read operation and tri-state the output pin (SO). The maximum SCK

frequency allowable for the continuous array read is defined by the fCAR1 specification. The continuous array read bypasses

both data buffers and leaves the contents of the buffers unchanged.

4.2 Continuous Array Read (High Frequency Mode: 0BH): Up to 66MHz

This command can be used with the serial interface to read the main memory array sequentially in high-speed mode for any

clock frequency up to the maximum specified by fCAR1. To perform a continuous read array with the page size set to 528 bytes,

CS must first be asserted, and then a 0BH opcode must be clocked into the device, followed by three address bytes and a

dummy byte. The first 13 bits (PA12 - PA0) of the 23-bit address sequence specify which page of the main memory array to

read, and the last 10 bits (BA9 - BA0) of the 23-bit address sequence specify the starting byte address within the page. To

perform a continuous read with the page size set to 512 bytes, the 0BH opcode must be clocked into the device, followed by

three address bytes (A21 - A0) and a dummy byte. Following the dummy byte, additional clock pulses on the SCK pin will result

in data being output on the SO (serial output) pin.

AT45DB321D [DATASHEET]

3597T–DFLASH–11/2013

5

5 Page

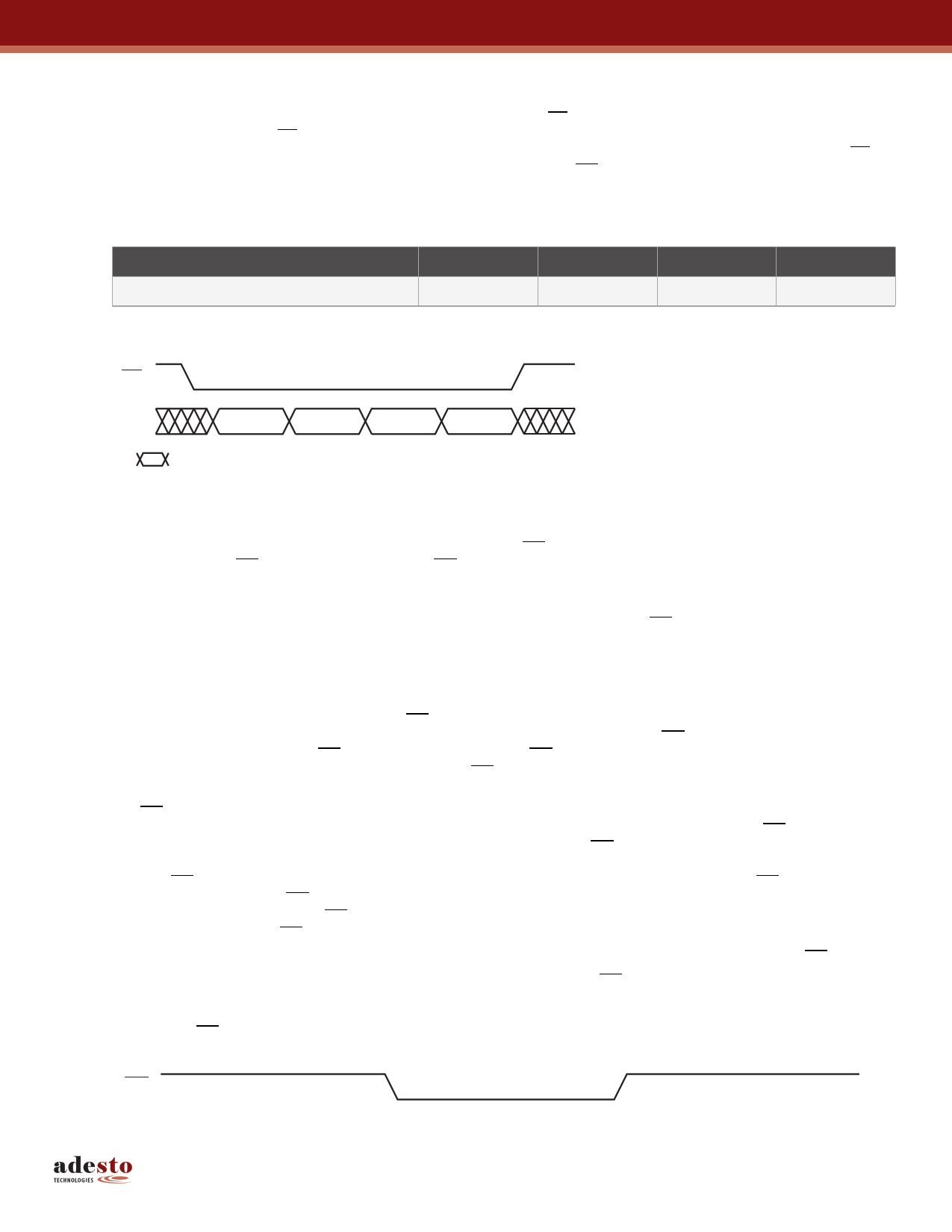

6.1.2

Disable Sector Protection Command

To disable sector protection using the software controlled method, the CS pin must first be asserted, as it would be with any

other command. Once the CS pin has been asserted, the appropriate four-byte sequence for the disable sector protection

command must be clocked in via the input pin (SI). After the last bit of the command sequence has been clocked in, the CS pin

must be deasserted, after which the sector protection will be disabled. The WP pin must be in the deasserted state; otherwise,

the disable sector protection command will be ignored.

Table 6-2. Disenable Sector Protection Command

Command

Disable sector protection

Byte 1

3DH

Byte 2

2AH

Byte 3

7FH

Byte 4

9AH

Figure 6-2. Disable Sector Protection

CS

SI

Opcode

Byte 1

Each transition

represents 8 bits

Opcode

Byte 2

Opcode

Byte 3

Opcode

Byte 4

6.1.3

Various Aspects About Software Controlled Protection

Software controlled protection is useful in applications in which the WP pin is not or cannot be controlled by a host processor. In

such instances, the WP pin may be left floating (the WP pin is internally pulled high), and sector protection can be controlled

using the enable sector protection and disable sector protection commands.

If the device is power cycled, then the software controlled protection will be disabled. Once the device is powered up, the enable

sector protection command should be reissued if sector protection is desired and if the WP pin is not used.

7. Hardware Controlled Protection

Sectors specified in the sector protection register for protection, and the sector protection register itself, can be protected from

program and erase operations by asserting the WP pin and keeping the pin in its asserted state. The sector protection register

and any sector specified for protection cannot be erased or reprogrammed as long as the WP pin is asserted. In order to modify

the sector protection register, the WP pin must be deasserted. If the WP pin is permanently connected to GND, then the content

of the sector protection register cannot be changed. If the WP pin is deasserted or permanently connected to VCC, then the

content of the sector protection register can be modified.

The WP pin will override the software controlled protection method, but only for protecting the sectors. For example, if the

sectors were not previously protected by the enable sector protection command, then simply asserting the WP pin would enable

sector protection within the maximum specified tWPE time. However, when the WP pin is deasserted, sector protection would no

longer be enabled (after the maximum specified tWPD time) as long as the enable sector protection command was not issued

while the WP pin was asserted. If the enable sector protection command was issued before or while the WP pin was asserted,

then simply deasserting the WP pin would not disable sector protection. In this case, the disable sector protection command

would need to be issued while the WP pin is deasserted to disable sector protection. The disable sector protection command is

also ignored whenever the WP pin is asserted.

A noise filter is incorporated to help protect against spurious noise that may inadvertently assert or deassert the WP pin.

The table below details the sector protection status for various scenarios of the WP pin, the enable sector protection command,

and the disable sector protection command.

Figure 7-1. WP Pin and Protection Status

1

WP

2

3

AT45DB321D [DATASHEET]

3597T–DFLASH–11/2013

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet AT45DB321D.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| AT45DB321 | 32-Megabit 2.7-volt Only Serial DataFlash | ATMEL Corporation |

| AT45DB321-CC | 32-Megabit 2.7-volt Only Serial DataFlash | ATMEL Corporation |

| AT45DB321-CI | 32-Megabit 2.7-volt Only Serial DataFlash | ATMEL Corporation |

| AT45DB321-TC | 32-Megabit 2.7-volt Only Serial DataFlash | ATMEL Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |