|

|

PDF FIN210AC Data sheet ( Hoja de datos )

| Número de pieza | FIN210AC | |

| Descripción | 10-Bit Serializer / Deserializer Supporting Cameras and Small Displays up to 48MHz | |

| Fabricantes | Fairchild Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de FIN210AC (archivo pdf) en la parte inferior de esta página. Total 17 Páginas | ||

|

No Preview Available !

June 2009

FIN210AC

10-Bit Serializer / Deserializer Supporting Cameras and

Small Displays up to 48MHz

Features

Data & Control Bits

Frequency

Capability

Interface

µController Usage

Selectable Edge Rates

Standby Current

Core Voltage (VDDA/S)

I/O Voltage (VDDP)

ESD (I/O to GND)

Package

Ordering Information

10-bit

48MHz

Camera or LCD

Microcontroller, RGB, YUV

m68 & i86

Yes

<10µA

2.8 to 3.6V

1.65 to 3.6V

15kV

32-Terminal MLP (Preliminary)

42-Ball USS-BGA

FIN210ACMLX (Preliminary)

FIN210ACGFX

Description

The FIN210AC µSerDes™ is a low-power serializer /

deserializer optimized for use in cell phone displays and

camera paths. The device reduces a 10-bit data path to four

wires. For camera applications, an additional master clock

can be passed in the opposite direction of data flow. The

device utilizes Fairchild’s proprietary ultra-low power, low-

EMI technology.

Applications

Slider, Folder, & Clamshell Mobile Handsets

Printers

Security Cameras

Typical Application

www.DataSheet4U.com

Baseband

Related Resources

For samples and questions, please contact:

FIN210AC

Internal

Termination

Built-in voltage

translation

FIN210AC

Camera

Module

+ 2+

-

-

2

++

--

CTL™

Isolates interface

for signal integrity

Camera

Module

Up to 48MHz

© 2009 Fairchild Semiconductor Corporation

FIN210AC • Rev. 1.0.1

Figure 1. Mobile Phone Example

www.fairchildsemi.com

1 page

Table 3. Deserializer S0 & S1 Control Pins (Note: All edge rates are typical values)

Slow Edge Rates

LVCMOS Output Edge Rates

~7 - 8ns (CL = 8pF)

S0

0

Medium Edge Rates

~4 - 5ns (CL = 8pF)

1

Fast Edge Rates

~2 - 3ns (CL = 8pF)

1

Power Down

0

S1

1

1

0

0

Pulse Width Calculations

CKP Pulse Width Low Time=(PLL Multiplier • Pwidth Multiplier) / (CKREF•12)

Example: CKREF=26MHz; PLL Multiplier=1; Pwidth Multiplier=6

CKP Pulse width=(1 • 6) / (26MHz • 12)=19.2ns

CKREF = Strobe 50% Duty Cycle

If CKREF = Strobe the below control states will provide a ~ 50% duty cycle pulse width output on CKP

Table 4. CKREF = Strobe 50% Duty Cycle

PLL0

1

Serializer

PLL1

0

PWS0

0

Deserializer

PWS1

0

(1)

(2)

Power-Down States

When both S1 and S0 signals are 0, regardless of the state of the DIRI signal, the FIN210AC resets and powers down. The

power-down mode shuts down all internal analog circuitry, disables the serial input and output of the device, and resets all

www.DaintateSrhneaelt4dUig.ictoaml logic. Table 5 indicates the state of the input states and output buffers in Power-Down mode.

Table 5. Power-Down

Signal Pins

DP[1:10]

CKP

STROBE

CKREF

/DIRO

DIRI=1 (Serializer)

Inputs Disabled

HIGH

Input Disabled

Input Disabled

0

DIRI=0 (Deserializer)

/ENZ = 0

Outputs High-Z

High-Z

Input Disabled

Input Disabled

1

DIRI=0 (Deserializer)

/ENZ = 1

Outputs Low

High

Input Disabled

Input Disabled

1

© 2009 Fairchild Semiconductor Corporation

FIN210AC • Rev. 1.0.1

5

www.fairchildsemi.com

5 Page

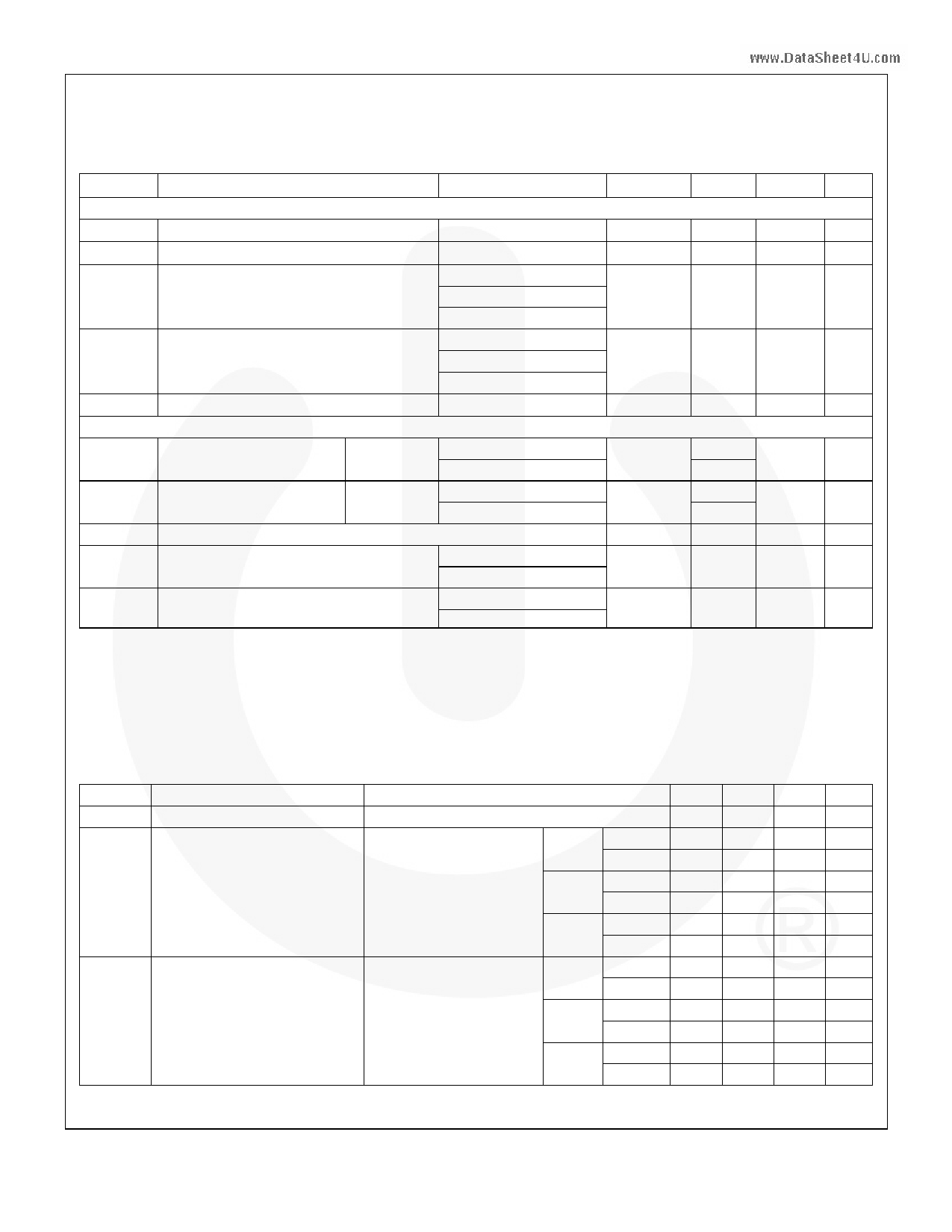

DC Electrical Characteristics

Values are provided for over-supply voltage and operating temperature ranges, unless otherwise specified.

Symbol

Parameter

Test Conditions

Min.

Typ.(3) Max. Unit

LVCMOS I/O

VIH Input High Voltage

VIL Input Low Voltage

VOH Output High Voltage

VOL Output Low Voltage

IIN Input Current

IOH=-2.0mA, S1=0,S0=1

IOH=-0.4mA, S1=1,S0=0

IOH=-1.0mA, S1=1,S0=1

IOL=2.0mA, S1=0,S0=1

IOL=0.4mA, S1=1,S0=0

IOL=1.0mA, S1=1,S0=1

VIN= 0V to 3.6V

0.65xVDDP

GND

0.75xVDDP

0

-5.0

VDDP

0.35xVDDP

V

VDDP

V

0.25xVDDP V

5.0 µA

DIFFERENTIAL I/O

IODH Output HIGH Source Current

VOS=1.0V

IODL

VGO

RTRM

Output LOW Sink Current

Input Voltage Ground Offset(4)

VOS=1.0V

CKS Internal Receiver Termination Resistor

DS Internal Receiver Termination Resistor

CTL_ADJ=0

CTL_ADJ=1

CTL_ADJ=0

CTL_ADJ=1

VID=50mV, VIC=925mV

DIRI=0

VID=50mV, VIC=925mV

DIRI=0

-4.1

mA

-5.3

2.1

mA

3.1

0V

80 100 120 Ω

80 100 120 Ω

Notes:

3. Typical values are given for VDD=2.775V and TA=25°C. Positive current values refer to the current flowing into the device

and negative values refer to the current flowing out of pins. Voltages are referenced to GROUND unless otherwise

specified (except ΔVOD and VOD).

4. VGO is the difference in device ground levels between the CTL driver and the CTL receiver.

www.DataSheet4U.com

Power Supply Currents

Symbol

IDD_PD

Parameter

VDD Power-Down Supply Current

Test Conditions

S1=S0=0, All Inputs at GND or VDD

S1=L

S0=H

IDD_SER1

Dynamic Serializer Power Supply

Current

fCKREF=fSTRB, PLL1=0,PLL0=1; S1=H

CTL_ADJ=0; CL=0pF

S0=L

S1=H

S0=H

S1=L

S0=H

IDD_DES1

Dynamic Deserializer Power Supply fCKREF=fSTRB, PLL1=0,PLL0=1; S1=H

Current

CTL_ADJ=0; CL=0pF

S0=L

S1=H

S0=H

20MHz

48MHz

5MHz

14MHz

8MHz

28MHz

20MHz

48MHz

5MHz

14MHz

8MHz

28MHz

Min.

Typ.

0.1

13

21

10

16

11

18

10

19

8

9

9

12

Max.

Unit

µA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

© 2009 Fairchild Semiconductor Corporation

FIN210AC • Rev. 1.0.1

11

www.fairchildsemi.com

11 Page | ||

| Páginas | Total 17 Páginas | |

| PDF Descargar | [ Datasheet FIN210AC.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| FIN210AC | 10-Bit Serializer / Deserializer Supporting Cameras and Small Displays up to 48MHz | Fairchild Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |