|

|

PDF ZL38070 Data sheet ( Hoja de datos )

| Número de pieza | ZL38070 | |

| Descripción | 256 Channel Voice Echo Canceller | |

| Fabricantes | Zarlink Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de ZL38070 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

Features

• ZL38070 has eight Echo Voice Processors in a

single BGA package. This single device provides

256 channels of 64 msec echo cancellation or

128 channels at 128 msec echo cancellation

• Each Echo Voice Processor has the capability of

cancelling echo over 32 channels

• Each Echo Voice Processor (EVP) shares the

address bus and data bus with each other

• Fully compliant to ITU-T G.165, G.168 (2000) and

(2002) specifications

• Passed all AT&T voice quality tests for carrier

grade echo canceller

• Sub 50 ms initial convergence times under many

typical network conditions

• Unparalleled in-system tunability

• The ZL38070 provides more than 58% board

space savings when compared with eight

individually packaged Echo Voice Processor

devices

• Each EVP has a Patented Advanced Non-Linear

Processor with high quality subjective

performance

• Each EVP has protection against narrow band

signal divergence and instability in high echo

environments

ZL38070

256 Channel Voice Echo Canceller

Data Sheet

January 2006

Ordering Information

ZL38070GBG 535 Ball BGA Trays, Bake & Drypack

ZL38070GBG2 535 Ball BGA** Trays, Bake & Drypack

**Pb Free Tin/Silver/Copper

-40°C to +85°C

• Each EVP can be programmed independently in

any mode e.g., Back-to-Back or Extended Delay

to provide capability of cancelling different echo

tails

• Each EVP has +9 to -12 dB level adjusters at all

signal ports (Rin, Sin, Sout and Rout)

• Parallel controller interface compatible with

Motorola microcontrollers

Applications

• Voice over IP network gateways

• Voice over ATM, Frame Relay

• T1/E1/J1 multichannel echo cancellation

• Wireless base stations

• Echo Canceller pools

• DCME, satellite and multiplexer system

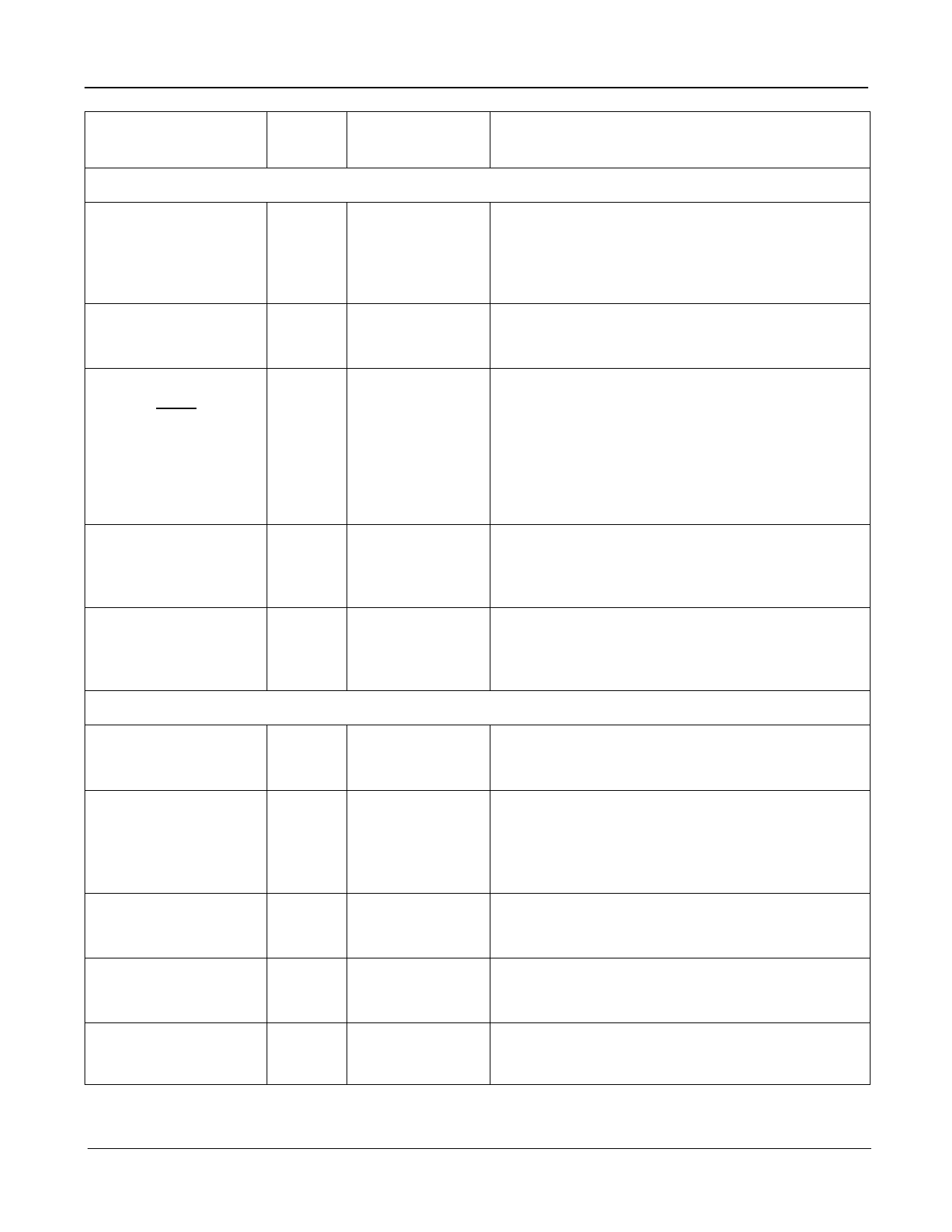

Rin1...Rin8

Sin1....Sin8

D0....D7

CS1..CS8

A0..A12

RESET1..RESET8

ZL38070GB

EVP1

EVP2

EVP3

EVP4

EVP5

EVP6

EVP7 EVP8

Rout1..Rout8

Sout1..Sout8

IRQ1..IRQ8

DTA1..DTA8

Figure 1 - ZL38070 Device Overview

1

Zarlink Semiconductor Inc.

Zarlink, ZL and the Zarlink Semiconductor logo are trademarks of Zarlink Semiconductor Inc.

Copyright 2004-2006, Zarlink Semiconductor Inc. All Rights Reserved.

1 page

ZL38070

Data Sheet

List of Tables

Table 1 - Quiet PCM Code Assignment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Table 2 - Memory Page Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Table 3 - Group and Channel Allocation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Table 4 - Memory Mapping of Per Channel Control and Status Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

5

Zarlink Semiconductor Inc.

5 Page

ZL38070

Data Sheet

Signal Name

Signal

Type

BGA Ball #

Signal Description

JTAG Signal Pins

TMS

TCK

TRST

TDI1,TDI2,TDI3,TDI4,

TDI5,TDI6,TDI7,TDI8

TDO1,TDO2,TDO3,

TDO4,TDO5,TDO6

TDO7,TDO8

JTAG

Signal

JTAG

Signal

JTAG

Signal

JTAG

Signals

JTAG

Signals

K2 Test Mode Select (3.3 V Input). JTAG signal that

controls the state transitions of the TAP controller. This

pin is pulled high by an internal pull-up when not

driven. This signal is connected to all processors. See

DC Electrical Characteristics, Note 1 on page 45.

D6 Test Clock (3.3 V Input). Provides the clock to the

JTAG test logic.This signal is connected to all

processors.

D7 Test Reset (3.3 V Input). Asynchronously initializes

the JTAG TAP controller by putting it in the Test-Logic-

Reset state. This pin should be pulsed low on power-

up or held low, to ensure that all the EVP’s are in the

normal functional mode. This pin is pulled by an

internal pull-down when not driven. This signal is

connected to all EVP’s. See DC Electrical

Characteristics, Note 1 on page 45.

K1,AK23,L2,AK2, Test Serial Data In (3.3 V Input). JTAG serial test

AJ3,AH20,F27,H27 instructions and data are shifted in on these pins.

These pins are pulled high by an internal pull-up when

not driven.

L1,AJ22,L4,AH4, Test Serial Data Out (Output). JTAG serial data is

AK3,AK24,J28,K28 outputted on these pins on the falling edge of TCK.

These pins are held in high impedance state when

JTAG scan is not enabled.

PLL Signal Pins

PLLVDD2 = 1.8V

PLLVSS1

PLLVSS2

T1M1, T1M2, T1M3,

T1M4, T1M5, T1M6,

T1M7, T1M8

T2M1, T2M2, T2M3,

T2M4, T2M5, T2M6,

T2M7, T2M8

SG1, SG2, SG3, SG4,

SG5, SG6, SG7, SG8

PLL

Power

H3,V1,H4,AE3,

AG2,AE26,D22,

C24, AE27

PLL Power Supply. Must be connected to PLLVDD2 =

1.8 V.

PLL

Power

J3,W2,H2,AF4, PLL Ground. Must be connected to VSS.

AF3,AF27,D24,

C25,AF26,H1,W4,

J2, AH1,AG3,AF22,

D25,E27,AF21

PLL Test D1,AH26,E1,AE1, Internal Connection. Connected to VSS for normal

Signals AD4,AK22,D18, operation.

C18

PLL Test F2,AG25,G3,AF1, Internal Connection. Connected to VSS for normal

Signals AD3,AF25,B18,A18 operation.

PLL Test G4,AJ25,F1,AE2, Internal Connection. Connected to VSS for normal

Signals

AG1,

operation.

AH25,B17,C17

11

Zarlink Semiconductor Inc.

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet ZL38070.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ZL38070 | 256 Channel Voice Echo Canceller | Zarlink Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |