|

|

PDF S70GL256M00 Data sheet ( Hoja de datos )

| Número de pieza | S70GL256M00 | |

| Descripción | Uniform Sector Flash Memory | |

| Fabricantes | SPANSION | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de S70GL256M00 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

S70GL256M00

256 Megabit (8 M x 32-Bit/16 M x 16-Bit)

MirrorBit™ 3.0 Volt-only Uniform Sector Flash Memory

with Versatile I/O™ Control

Data Sheet (Retired Product)

S70GL256M00 Cover Sheet

This product has been retired and is not recommended for designs. For new and current designs,

S29GL256N supersedes S70GL256M and is the factory-recommended migration path for this device.

Please refer to the S29GL256N Datasheet for specifications and ordering information. Availability of this

document is retained for reference and historical purposes only.

Notice to Readers: This document states the current technical specifications regarding the Spansion

product(s) described herein. The Preliminary status of this document indicates that product qualification has

been completed, and that initial production has begun. Due to the phases of the manufacturing process that

require maintaining efficiency and quality, this document may be revised by subsequent versions or

modifications due to changes in technical specifications.

Publication Number S70GL256M00_00 Revision A Amendment 1

Issue Date October 31, 2006

1 page

DATA SHEET

TABLE OF CONTENTS

Product Selector Guide . . . . . . . . . . . . . . . . . . . . . 4

MCP Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . 4

Flash Memory Block diagram . . . . . . . . . . . . . . . . 5

Special Package Handling Instructions .................................... 6

Pin Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Logic Symbols . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

x16 Mode .................................................................................. 7

x32 Mode .................................................................................. 7

Ordering Information . . . . . . . . . . . . . . . . . . . . . . . 8

Device Bus Operations . . . . . . . . . . . . . . . . . . . . . 9

Table 1. Device Bus Operations ....................................................... 9

Word/Byte Configuration .......................................................... 9

VersatileIOTM (VIO) Control ........................................................ 9

Requirements for Reading Array Data ................................... 10

Page Mode Read ............................................................................10

Writing Commands/Command Sequences ............................ 10

Write Buffer .....................................................................................10

Accelerated Program Operation ......................................................10

Autoselect Functions .......................................................................10

Standby Mode ........................................................................ 10

Automatic Sleep Mode ........................................................... 11

RESET#: Hardware Reset Pin ............................................... 11

Output Disable Mode .............................................................. 11

Table 2. Sector Address Table........................................................ 12

Autoselect Mode ..................................................................... 18

Table 3. Autoselect Codes, (High Voltage Method) ....................... 18

Sector Group Protection and Unprotection ............................. 19

Table 4. Sector Group Protection/Unprotection Address Table ..... 19

Write Protect (WP#) ................................................................ 20

Temporary Sector Group Unprotect ....................................... 20

Figure 1. Temporary Sector Group Unprotect Operation ................20

Figure 2. In-System Sector Group Protect/Unprotect Algorithms ...21

SecSi (Secured Silicon) Sector Flash Memory Region .......... 22

Table 5. SecSi Sector Contents ...................................................... 22

Figure 3. SecSi Sector Protect Verify ..............................................23

Hardware Data Protection ...................................................... 23

Low VCC Write Inhibit .....................................................................23

Write Pulse “Glitch” Protection ........................................................23

Logical Inhibit ..................................................................................23

Power-Up Write Inhibit ....................................................................23

Common Flash Memory Interface (CFI) . . . . . . . 23

Reading Array Data ................................................................ 27

Reset Command ..................................................................... 27

Autoselect Command Sequence ............................................ 27

Enter SecSi Sector/Exit SecSi Sector Command Sequence .. 28

Doubleword/Word Program Command Sequence ................. 28

Unlock Bypass Command Sequence ..............................................28

Write Buffer Programming ...............................................................28

Accelerated Program ......................................................................29

Figure 4. Write Buffer Programming Operation ...............................30

Figure 5. Program Operation ..........................................................31

Program Suspend/Program Resume Command Sequence ... 31

Figure 6. Program Suspend/Program Resume ...............................32

Chip Erase Command Sequence ........................................... 32

Sector Erase Command Sequence ........................................ 32

Figure 7. Erase Operation .............................................................. 33

Erase Suspend/Erase Resume Commands ........................... 33

Command Definitions ............................................................. 34

Write Operation Status . . . . . . . . . . . . . . . . . . . . . 36

DQ7 and DQ5: Data# Polling .................................................. 36

Figure 8. Data# Polling Algorithm .................................................. 36

RY/BY#: Ready/Busy# ............................................................ 37

DQ6 and DQ14: Toggle Bits I ................................................. 37

Figure 9. Toggle Bit Algorithm ........................................................ 38

DQ2 and DQ10: Toggle Bits II ................................................ 38

Reading Toggle Bits DQ6 and DQ14/DQ2 and DQ10 ............ 38

DQ5 and DQ13: Exceeded Timing Limits ............................... 39

DQ3 and DQ11: Sector Erase Timer ...................................... 39

DQ1: Write-to-Buffer Abort ..................................................... 40

Table 12. Write Operation Status................................................... 40

Figure 10. Maximum Negative Overshoot Waveform .................... 41

Figure 11. Maximum Positive Overshoot Waveform ...................... 41

Operating Ranges . . . . . . . . . . . . . . . . . . . . . . . . . 41

DC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . 42

Figure 12. Test Setup ..................................................................... 43

Table 13. Test Specifications ......................................................... 43

Key to Switching Waveforms. . . . . . . . . . . . . . . . 43

Figure 13. Input Waveforms and

Measurement Levels ...................................................................... 43

AC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . 44

Read-Only Operations ............................................................ 44

Figure 14. Read Operation Timings ............................................... 44

Figure 15. Page Read Timings ...................................................... 45

Hardware Reset (RESET#) .................................................... 46

Figure 16. Reset Timings ............................................................... 46

Erase and Program Operations .............................................. 47

Figure 17. Program Operation Timings .......................................... 48

Figure 18. Accelerated Program Timing Diagram .......................... 48

Figure 19. Chip/Sector Erase Operation Timings .......................... 49

Figure 20. Data# Polling Timings (During Embedded Algorithms) . 50

Figure 21. Toggle Bit Timings (During Embedded Algorithms) ...... 51

Figure 22. DQ2 vs. DQ6 ................................................................. 51

Temporary Sector Unprotect .................................................. 52

Figure 23. Temporary Sector Group Unprotect Timing Diagram ... 52

Figure 24. Sector Group Protect and Unprotect Timing Diagram .. 53

Alternate CE# Controlled Erase and Program Operations ..... 54

Figure 25. Alternate CE# Controlled Write (Erase/Program)

Operation Timings ...............................................................................55

Latchup Characteristics . . . . . . . . . . . . . . . . . . . . 55

Erase And Programming Performance. . . . . . . . 56

TSOP Pin and BGA Package Capacitance . . . . . 56

LSB080–80-Ball Fortified Ball Grid Array (Fortified BGA)

13 x 11 mm Package .............................................................. 57

Revision Summary . . . . . . . . . . . . . . . . . . . . . . . . 58

October 31, 2006 S70GL256M00_00_A1

S70GL256M00

3

5 Page

DATA SHEET

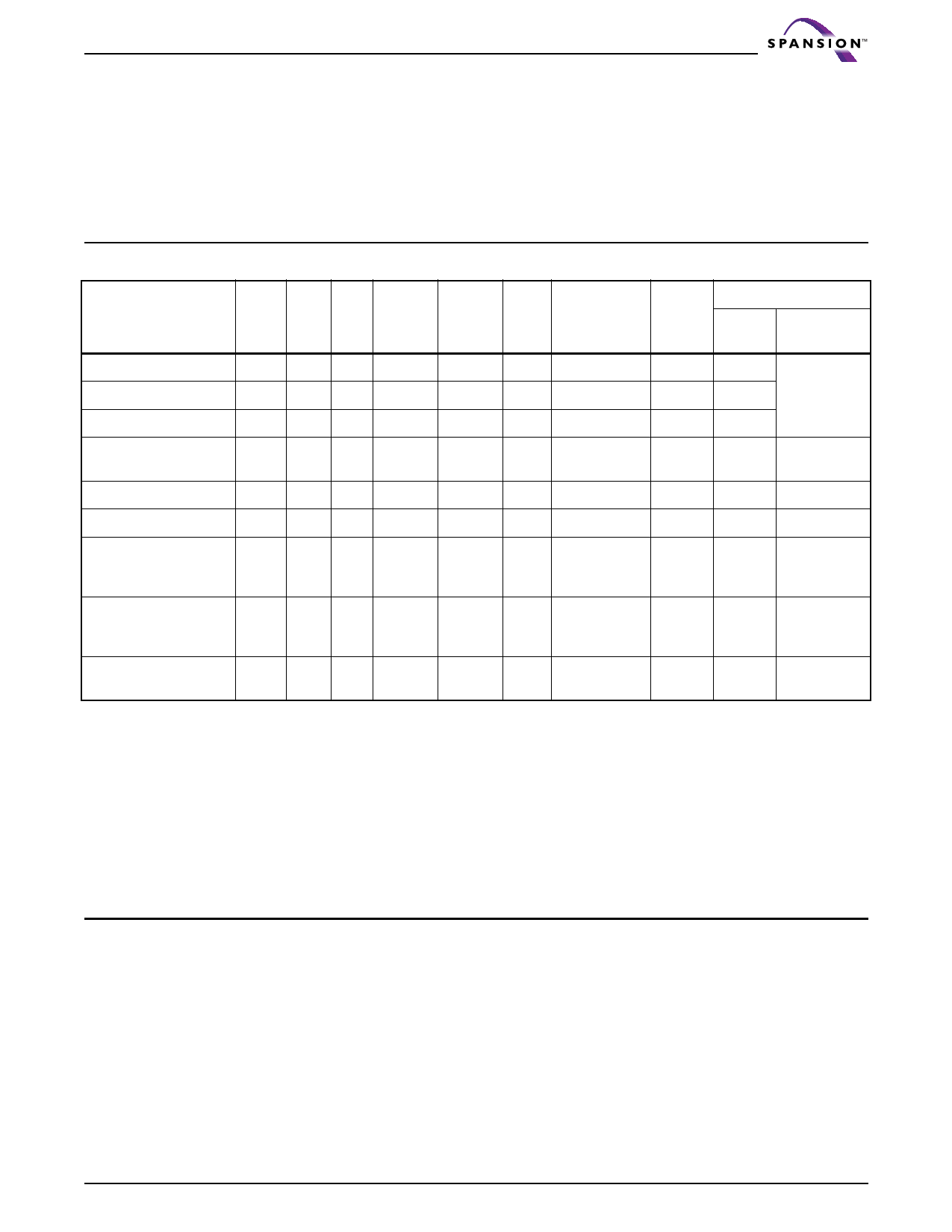

DEVICE BUS OPERATIONS

This section describes the requirements and use of

the device bus operations, which are initiated through

the internal command register. The command register

itself does not occupy any addressable memory loca-

tion. The register is a latch used to store the com-

mands, along with the address and data information

needed to execute the command. The contents of the

register serve as inputs to the internal state machine.

The state machine outputs dictate the function of the

device. Table 1 lists the device bus operations, the in-

puts and control levels they require, and the resulting

output. The following subsections describe each of

these operations in further detail.

Table 1. Device Bus Operations

DQ31–DQ16

Operation

Read

Write (Program/Erase)

Accelerated Program

Standby

Output Disable

Reset

CE# OE# WE# RESET# WP# ACC

L LH

H

XX

L HL

H (Note 3) X

L

VCC ±

0.3 V

H

X

L H (Note 3) VHH

X

VCC ±

0.3 V

X

H

L HH

H

XX

X XX

L

XX

Addresses

(Note 1)

AIN

AIN

AIN

DQ15– WORD#

DQ0

= VIH

WORD#

= VIL

DOUT

(Note 4)

(Note 4)

DOUT

(Note 4)

(Note 4)

DQ31–DQ16

= High-Z,

DQ31 &

DQ23= A-1

X

High-Z High-Z

High-Z

X

High-Z High-Z

High-Z

X

High-Z High-Z

High-Z

Sector Group Protect

(Note 2)

L

Sector Group Unprotect

(Note 2)

Temporary Sector Group

Unprotect

L

X

HL

HL

XX

VID

VID

VID

SA, A6 =L,

H X A3=L, A2=L, (Note 4) X

A1=H, A0=L

SA, A6=H,

H X A3=L, A2=L, (Note 4) X

A1=H, A0=L

X

X

HX

AIN (Note 4) (Note 4) High-Z

Legend: L = Logic Low = VIL, H = Logic High = VIH, VID = 11.5–12.5 V, VHH = 11.5–12.5V, X = Don’t Care, SA = Sector Address,

AIN = Address In, DIN = Data In, DOUT = Data Out

Notes:

1. Addresses are A22:A0 in doubleword mode; A22:A-1 in word mode. Sector addresses are A22:A15 in both modes.

2. The sector group protect and sector group unprotect functions may also be implemented via programming equipment. See the

“Sector Group Protection and Unprotection” section.

3. If WP# = VIL, the first or last sector group remains protected. If WP# = VIH, the first or last sector will be protected or unprotected as

determined by the method described in “Write Protect (WP#)”. All sectors are unprotected when shipped from the factory (The

SecSi Sector may be factory protected depending on version ordered.)

4. DIN or DOUT as required by command sequence, data polling, or sector protect algorithm (see Figure 2).

Word/Byte Configuration

The WORD# pin controls whether the device data I/O

pins operate in the word or doubleword configuration.

If the WORD# pin is set at VIH, the device is in double-

word configuration, DQ31–DQ0 are active and con-

trolled by CE# and OE#.

If the WORD# pin is set at VIL, the device is in word

configuration, and only data I/O pins DQ15–DQ0 are

active and controlled by CE# and OE#. The data I/O

pins DQ31–DQ16 are tri-stated, and the DQ23 and

DQ31 pins are used as inputs for the LSB (A-1) ad-

dress function.

VersatileIOTM (VIO) Control

The VersatileIOTM (VIO) control allows the host system

to set the voltage levels that the device generates and

tolerates on CE# and DQ I/Os to the same voltage

level that is asserted on VIO. See Ordering Information

for VIO options on this device.

October 31, 2006 S70GL256M00_00_A1

S70GL256M00

9

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet S70GL256M00.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| S70GL256M00 | Uniform Sector Flash Memory | SPANSION |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |