|

|

PDF OX16C950 Data sheet ( Hoja de datos )

| Número de pieza | OX16C950 | |

| Descripción | High Performance UART | |

| Fabricantes | Oxford Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de OX16C950 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

OX16C950 rev B

High Performance UART

with 128 byte FIFOs

FEATURES

• Single full-duplex asynchronous channel

• 128-byte deep transmitter / receiver FIFO

• Fully software compatible with industry standard

16C550 type UARTs

• Pin compatible with TL16C550B/C, ST16C650 and

TL16C750

• IBM PC/AT compatible

• Baud rates up to 15 Mbps in normal mode and

60Mbps in external 1x clock mode

• Readable FIFO levels

• Flexible clock prescaler from 1 to 31.875

• Isochronous mode using external 1x baud rate clock

up to 60Mbps

• 9-bit data framing as well as 5,6,7 and 8

• Detection of bad data in the receiver FIFO

• Automated in-band flow control using programmable

Xon/Xoff characters

• Transmitter and receiver can be disabled

• Automated out-of-band flow control using CTS# / RTS#

and DSR# / DTR#

• Readable in-band and out-of-band flow control status

• Programmable special character detection

• Arbitrary trigger levels for receiver and transmitter FIFO

interrupts and automatic in-band and out-of-band flow

control

• Transmitter idle interrupt (shift register and FIFO both

empty)

• Optional Infra-red (IrDA) receiver and transmitter

operation

• RS-485 buffer enable signals

• Software channel reset

• Four byte device ID

• Sleep mode (low operating current)

• System clock up to 60 MHz (at 5V), 50 MHz at 3.3V

• 44 PLCC and 48 TQFP packages

• 5 volts operation (PLCC), 3.3/ 5V operation TQFP

REV B ENHANCEMENTS

The OX16C950B is an enhanced, fully backward-compatible revision of the OX16C950 rev A. The chief enhancements are as

follows –

• All known errata fixed

• Enhanced features first offered in OX16PCI954 added – these include controls for sleep-mode sensitivity, ability to

read FCR and Good Data Status

• 3V operation possible with 48 pin TQFP

• Enhanced isochronous clocking options (optional inversions)

• Enhanced system clock selection options (use of CLKSEL as a clock input)

• Readable TxRdy, RxRdy status and forcing TxRdy or RxRdy inactive

Hereafter OX16C950 rev B is simply referred to as OX16C950.

Oxford Semiconductor Ltd.

25 Milton Park, Abingdon, Oxon, OX14 4SH, UK

Tel: +44 (0)1235 824900 Fax: +44 (0)1235 821141

Oxford Semiconductor 2001

OX16C950 rev B Datasheet R1.2 – May 2001

Part No. OX16C950-PCC60-B

1 page

OXFORD SEMICONDUCTOR LTD.

OX16C950 rev B

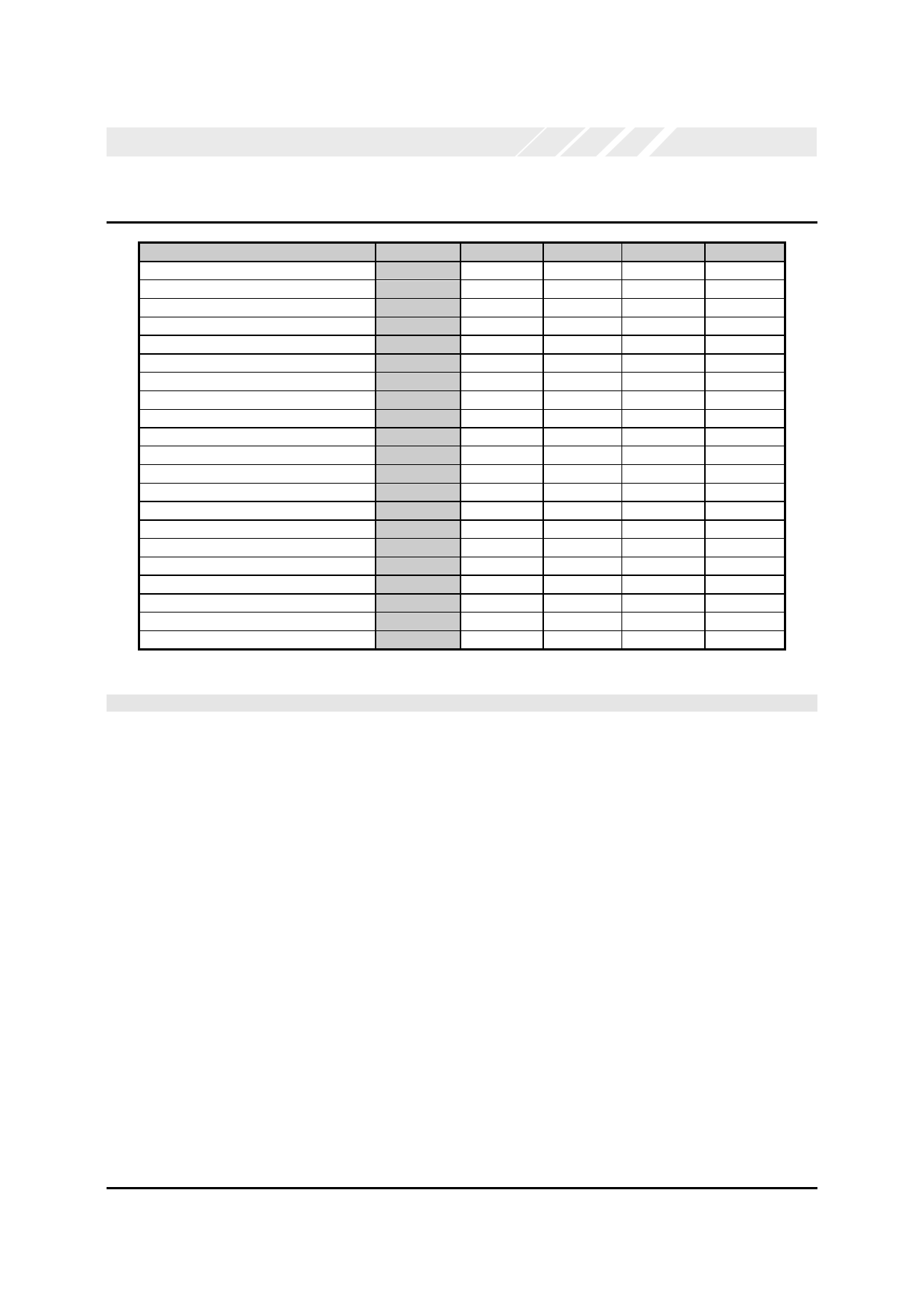

1 PERFORMANCE COMPARISON

Feature

External 1x baud rate clock

Max baud rate in normal mode

Max baud rate in 1x clock mode

FIFO depth

Sleep mode

Auto Xon/Xoff flow

Auto CTS#/RTS# flow

Auto DSR#/DTR# flow

No. of Rx interrupt thresholds

No. of Tx interrupt thresholds

No. of flow control thresholds

Transmitter empty interrupt

Readable status of flow control

Readable FIFO levels

Clock prescaler options

Rx/Tx disable

Software reset

Device ID

9-bit data frames

RS485 buffer enable

Infra-red (IrDA)

OX16C950

Yes

15 Mbps

60 Mbps

128

Yes

Yes

Yes

Yes

127

128

128

Yes

Yes

Yes

248

Yes

Yes

Yes

Yes

Yes

Yes

16C450

No

115 kbps

n/a

1

No

No

No

No

1

1

n/a

No

n/a

n/a

n/a

No

No

No

No

No

No

16C550

No

115 kbps

n/a

16

No

No

No

No

4

1

n/a

No

No

No

n/a

No

No

No

No

No

No

16C650

No

1.5 Mbps

n/a

32

Yes

Yes

Yes

No

4

4

4

No

No

No

2

No

No

No

No

No

Yes

16C750

No

1 Mbps

n/a

64

Yes

No

Yes

No

4

1

n/a

No

No

No

n/a

No

No

No

No

No

No

Table 1 OX16C950 performance compared with 16C450, 16C550, 16C650 and 16C750 devices

Improvements of the OX16C950 over previous generations of PC UART:

Deeper FIFOs:

OX16C950 offers 128-byte deep FIFOs for the transmitter

and receiver.

Higher data rates:

Transmission and reception baud rates up to 15Mbps. A

flexible clock prescaler offers division ratios of 1 to 31 7/8

in steps of 1/8 using a divide-by-“M N/8” circuitry. The

flexible prescaler allows users to select from a wide variety

of input clock frequencies as well as access to higher baud

rates whilst maintaining compatibility with existing software

drivers (see section 14.2).

Special character detection:

The receiver can be programmed to generate an interrupt

upon reception of a particular character value.

Power-down:

The device can be placed in ‘sleep mode’ to conserve

power.

Readable FIFO levels:

Driver efficiency can be improved by using readable FIFO

levels.

External clock options:

The receiver can accept an external 1x clock on the DSR#

input. The transmitter can accept a 1x clock on the RI#

input and/or assert its own (Nx) clock on the DTR# output.

In 1x mode, asynchronous data may be transmitted and

received at speeds up to 60Mbps (see section 14.6).

Automatic flow control:

The UART automatically handles either or both in-band

(software) flow control (transmitting and receiving Xon/Xoff

characters) and out-of-band (hardware) flow control using

the RTS#/CTS# or DSR#/DTR# modem control lines.

Selectable trigger levels:

The receiver FIFO threshold can be arbitrarily

programmed. The transmitter FIFO threshold and

thresholds for automatic flow control can be programmed

to operate at a variety of trigger levels.

Additional control:

The transmitter and receiver can be independently

disabled.

Data Sheet Revision 1.2

Page 5

5 Page

OXFORD SEMICONDUCTOR LTD.

OX16C950 rev B

4.1 Further Pin Information

Pin

CS0

CS1

CS2#

IOR

IOW

Description

Chip Select

Chip Select

Chip Select

Additional I/O Read Control

Additional I/O Write Control

INTSEL# Interrupt Control Mode

RXRDY# DMA Control signal output

TXRDY# DMA Control signal output

BDOUT# Baud rate generator output

RCLK

XTLI

XTLO

Receiver clock input

Crystal circuit input

Crystal circuit output

Action when used

Action when not used

Bus Interface Pins

Connect to active high chip select generation Tie high – All chip selects must be

logic active in order to access the device

Connect to active high chip select generation Tie high – All chip selects must be

logic active in order to access the device

Connect to active low chip select generation Tie low – All chip selects must be active

logic in order to access the device

Connect to processors active high I/O read Tie low (IOR# will be used to control I/O

line (and tie IOR# high)

read operations)

Connect to processors active high I/O write Tie low (IOW# will be used to control

line (and tie IOW# high)

I/O read operations)

Control Pins

Tie low to allow software enable/disable of the Leave unconnected (Pulled high

interrupt pin.

internally to leave the interrupt pin

permanently enabled).

DMA Pins

Connect direct to DMA control circuitry

Leave unconnected

Connect direct to DMA control circuitry

Leave unconnected

Clock Related Pins

Connect direct to the RCLK pin in order to run Leave unconnected

the receiver with the same clock as the

transmitter

Connect directly to a suitable receiver clock

source (Usually the BDOUT# pin)

n/a

Connect to suitable clock input

n/a

Connect to crystal oscillator circuit

Leave unconnected

DDIS

ADS#

OUT1#

OUT2#

SOUT

SIN

RTS#

CTS#

DTR#

DSR#

Miscellaneous Pins

Driver Disable output

Connect to active high bus transceiver drive Leave unconnected

disable (goes high when device is not being

read from)

Address Strobe In

Connect direct to external control circuitry Tie low

(Low-High transition on this pin latches CS0-2

and A0-2)

User defined output

Connect direct to TTL input of external circuit Leave unconnected

to control

User defined output

Connect direct to TTL input of external circuit Leave unconnected

to control

Common Channel Pins

Serial data output

Connect to a suitable line driver

Leave unconnected

(Serial data can not be transmitted)

Serial data input

Connect to a suitable line receiver

Leave unconnected

(Serial data can not be received)

Request-To-Send Modem Connect to a suitable line driver

Leave unconnected

signal output

Clear-To-Send Modem signal Connect to a suitable line receiver

Tie high

input

Data-Terminal-Ready

Connect to a suitable line driver

Leave unconnected

Modem signal output

Data-Set-Ready

Connect to a suitable line receiver

Tie high

Modem signal input

Data Sheet Revision 1.2

Page 11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet OX16C950.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| OX16C950 | High Performance UART | Oxford Semiconductor |

| OX16C950B | Intelligent Single Channel UART | Oxford Semiconductor |

| OX16C954 | High Performance Quad UART with 128-byte FIFOs Intel / Motorola Bus Interface | ETC |

| OX16C95X | HIGH-PERFORMANCE UART FAMILY REFERENCE DRIVERS | Oxford Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |