|

|

PDF T224160B Data sheet ( Hoja de datos )

| Número de pieza | T224160B | |

| Descripción | 256K x 16 DYNAMIC RAM FAST PAGE MODE | |

| Fabricantes | Taiwan Memory Technology | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de T224160B (archivo pdf) en la parte inferior de esta página. Total 14 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

tm TE

CH

DRAM

T224160B

256K x 16 DYNAMIC RAM

FAST PAGE MODE

FEATURES

• Industry-standard x 16 pinouts and timing

functions.

• Single 5V (±10%) power supply.

• All device pins are TTL- compatible.

• 512-cycle refresh in 8ms.

• Refresh modes: RAS only, CAS BEFORE

RAS (CBR) and HIDDEN.

• Conventional FAST PAGE MODE access cycle.

• BYTE WRITE and BYTE READ access

cycles.

OPTION

TIMING

30ns

35ns

45ns

60ns

MARKING

-30

-35

-45

-60

will write data into the upper byte (IO9~16).

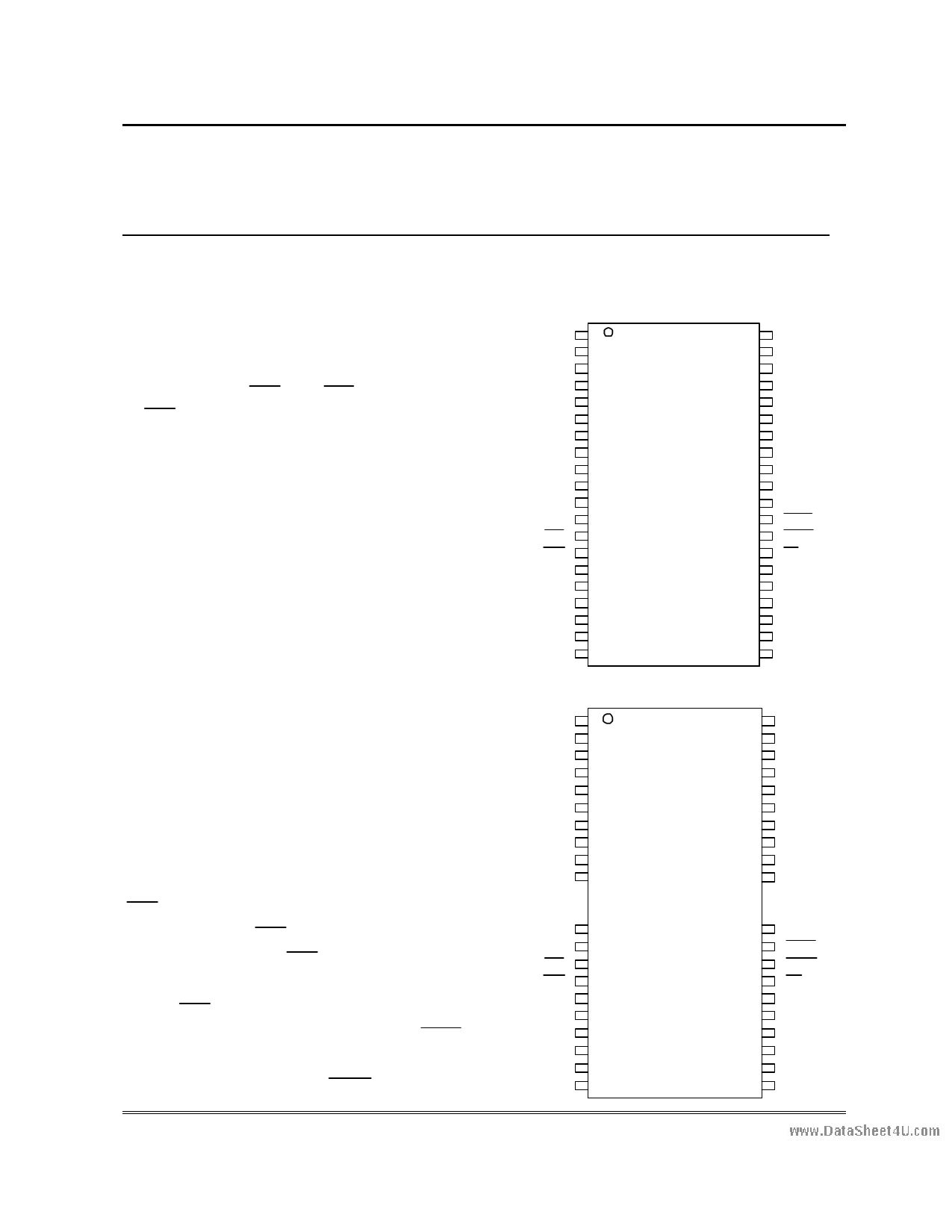

PIN ASSIGNMENT ( Top View )

Vcc

I/01

I/02

I/03

I/04

Vcc

I/05

I/06

I/07

I/08

NC

NC

WE

RAS

NC

A0

A1

A2

A3

Vcc

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

SOJ

40 Vss

39 I/016

38 I/015

37 I/014

36 I/013

35 Vss

34 I/012

33 I/011

32 I/010

31 I/09

30 NC

29 CASL

28 CASH

27 OE

26 A8

25 A7

24 A6

23 A5

22 A4

21 VSS

PACKAGE

SOJ

TSOP(II)

MARKING

J

S

GENERAL DESCRIPTION

The T224160B is a randomly accessed solid state

memory containing 4,194,304 bits organized in a x16

configuration. The T224160B has both BYTE

WRITE and WORD WRITE access cycles via two

CAS pins. It offers Fast Page mode operation

The T224160B CAS function and timing are

determined by the first CAS to transition low and

by the last to transition back high. Use only one of

the two CAS and leave the other staying high during

WRITE will result in a BYTE WRITE. CASL

transiting low in a WRITE cycle will write data into

the lower byte (IO1~IO8), and CASH transiting low

Taiwan Memory Technology, Inc. reserves the right P. 1

to change products or specifications without notice.

Vcc 1

I/01 2

I/02 3

I/03 4

I/04 5

Vcc 6

I/05 7

I/06 8

I/07 9

I/08 10

NC

NC

WE

RAS

NC

A0

A1

A2

A3

Vcc

11

12

13

14

15

16

17

18

19

20

TSOP(II)

40 Vss

39 I/016

38 I/015

37 I/014

36 I/013

35 Vss

34 I/012

33 I/011

32 I/010

31 I/09

30 NC

29 CASL

28 CASH

27 OE

26 A8

25 A7

24 A6

23 A5

22 A4

21 VSS

Publication Date: MAR. 2001

Revision:B

DataSheet4 U .com

1 page

www.DataSheet4U.com

tm TE

CH

T224160B

AC CHARACTERISTICS (note 1,2,3) (Ta = 0 to 70°C)

AC TEST CONDITIONS:

Vcc=5V ±10%, input pulse level = 0 to 3V

Input rise and fall times: 2ns

Output Load: 2TTL gate + CL (50pF)

AC CHARACTERISTICS

PARAMETER

SYM

-30 -35 -45 -60 UNIT Note

MIN MAX MIN MAX MIN MAX MIN MAX

s

Read or Write Cycle Time

Read-Modify-Write Cycle Time

Fast-Page-Mode Read or Write Cycle Time

Fast-Page-Mode Read-Write Cycle Time

Access Time From RAS

tRC 55 65 85 110 ns

tRWC 85 95 115 155 ns

tPC 19 21 25 40 ns

tPCM 56 58 65 80 ns

tRAC 30 35 45 60 ns 4

Access Time From CAS

tCAC

8

9 11 15 ns 5

Access Time From OE

tOAC

8

9 11 15 ns 13

Access Time From Column Address

Access Time From CAS Precharge

tAA 13 15 19 30 ns 8

tACP

15 18 22

35 ns

RAS Pulse Width

tRAS 30 10K 35 10K 45 10K 60 10K ns

RAS Pulse Width

tRASC 30 100K 35 100K 45 100K 60 100K ns

RAS Hold Time

tRSH 8 9 11 15 ns

RAS Precharge Time

tRP 25 30 35 40 ns

CAS Pulse Width

tCAS 5 10K 6 10K 7 10K 15 10K ns

CAS Hold Time

tCSH 30 35 45 60 ns

CAS Precharge Time

tCP 3 3 5 10 ns

RAS to CAS Delay Time

tRCD 10 24 10 28 10 37 20 45 ns 7

CAS to RAS Precharge Time

tCRP 3 3 5 5 ns

Row Address Setup Time

Row Address Hold Time

RAS to Column Address Delay Time

tASR 0 0 0 0 ns

tRAH 5 5 5 5 ns

tRAD 8 17 8 20 8 26 15 30 ns 8

Column Address Setup Time

tASC 0 0 0 0 ns

Column Address Hold Time

tCAH 4 4 6 15 ns

Column Address Hold Time (Reference to

RAS )

tAR 26

30

40

50

ns

Column Address to RAS Lead Time

tRAL 13 15 19 30 ns

Read Command Setup Time

tRCS 0 0 0 0 ns 14

Read Command Hold Time Reference to CAS tRCH 0 0 0 0 ns 9,14

Read Command Hold Time Reference to RAS tRRH 0 0 0 0 ns 9

CAS to Output in Low -Z

tCLZ 3 3 3 3 ns

Output Buffer Turn-off Delay From CAS or

RAS

ns 10,16

tOFF1 3 15 3 15 3 15 3 15

Taiwan Memory Technology, Inc. reserves the right P. 5

to change products or specifications without notice.

Publication Date: MAR. 2001

Revision:B

DataSheet4 U .com

5 Page

www.DataSheet4U.com

tm TE

CH

T224160B

RAS

VIH

VIL

CAS

VIH

VIL

ADDR

VIH

VIL

WE VVIIHL

I/O

VIOH

VIOL

OE

VIH

VIL

FAST-PAGE-MODE READ-EARLY-WRITE CYCLE

(Pseudo READ-MODIFY-WRITE)

tRASC

tCRP

tCSH

tRCD

tPC

tC AS

tPC

tCP tCAS

tCP

tRSH

tCAS

tRAD

tASR tR AH

ROW

tAR

tASC

tCAH

COLUMN( A)

tRCS

tASC tC AH

COLUMN(B)

tRCH

tRAL

tASC tCAH

COLUMN( N)

tWCS

tWCH

t AA

tRAC

tCAC

OPEN

tO AC

tACP

tOFF1

tCLZ

VALID

DATA (A)

t AA

tCAC

tOF F1

tDS tDH

VALID

VALID

DATA (B) NOTE1 DATA IN

tRP

tCP

ROW

RAS

VVII

H

L

CA S

VVII

H

L

A D DR

VVII

H

L

I /O

V

V

OH

OL

RAS ONLY REFRESH CYCLE

(ADDR=A0-A8 ; OE , WE =DON‘T CARE)

tCRP

tASR

tR A H

ROW

tR A S

t RC

tR P

tR PC

OP EN

Note1:Do not drive data prior to tristate.

RO W

DON'T CARE

UNDEFINED

Taiwan Memory Technology, Inc. reserves the right P. 11

to change products or specifications without notice.

DataSheet4 U .com

Publication Date: MAR. 2001

Revision:B

11 Page | ||

| Páginas | Total 14 Páginas | |

| PDF Descargar | [ Datasheet T224160B.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| T224160B | 256K x 16 DYNAMIC RAM FAST PAGE MODE | Taiwan Memory Technology |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |