|

|

PDF MK2049-02 Data sheet ( Hoja de datos )

| Número de pieza | MK2049-02 | |

| Descripción | Communications Clock PLLs | |

| Fabricantes | Integrated Circuit Systems | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de MK2049-02 (archivo pdf) en la parte inferior de esta página. Total 12 Páginas | ||

|

No Preview Available !

MK2049-02/03

Communications Clock PLLs

Description

The MK2049-02 and MK2049-03 are Phase-

Locked Loop (PLL) based clock synthesizers that

accept multiple input frequencies. With an 8 kHz

clock input as a reference, the MK2049-02/03

generate T1, E1, T3, E3, ISDN, xDSL, and other

communications frequencies. This allows for the

generation of clocks frequency-locked and phase-

locked to an 8 kHz backplane clock, simplifying

clock synchronization in communications systems.

The MK2049-02/03 can also accept a T1, E1, T3,

or E3 input clock and provide the same output for

loop timing. All outputs are frequency-locked

together and to the input.

These parts also have a jitter-attenuated buffer

capability. In this mode, the MK2049-02/03 are

ideal for filtering jitter from 27 MHz video clocks

or other clocks with high jitter.

ICS/MicroClock can customize these devices for

many other different frequencies. Contact your

ICS/MicroClock representative for more details.

Features

• Packaged in 20 pin SOIC

• Fixed input-output phase relationship on most

clock selections

• Meets the TR62411, ETS300 011, and GR-1244

specification for MTIE, Pull-in/Hold-in Range,

Phase Transients, and Jitter Generation for

Stratum 3, 4, and 4E

• Accept multiple inputs: 8 kHz backplane clock,

Loop Timing frequencies, or 10-28 MHz

• Lock to 8 kHz ±100 ppm (External mode)

• Buffer Mode allows jitter attenuation of

10–28 MHz input and x1/x0.5 or x2/x4 outputs

• Exact internal ratios enable zero ppm error

• Output clock rates include T1, E1, T3, E3, ISDN,

xDSL, and OC3 submultiples

• 5 V ±5% operation. Refer to MK2049-34 for 3.3 V

Block Diagram

VDD

4

GND

3

RESET

FS3:0 4

Clock

Input

Reference

Crystal X1

External/

Loop Timing

Mux

Crystal

Oscillator

PLL

Clock

Synthesis,

Control, and

Jitter

Attenuation

Circuitry

X2

CAP1

CAP2

Output

Buffer

Output

Buffer

Output

Buffer

CLK1

CLK2

CLK3

8 kHz

(External

Mode only)

MDS 2049-02/03 B

1

Revision 040601

Integrated Circuit Systems, Inc. • 525 Race Street • San Jose • CA • 95126 • (408)295-9800tel• www.icst.com

1 page

MK2049-02/03

Communications Clock PLLs

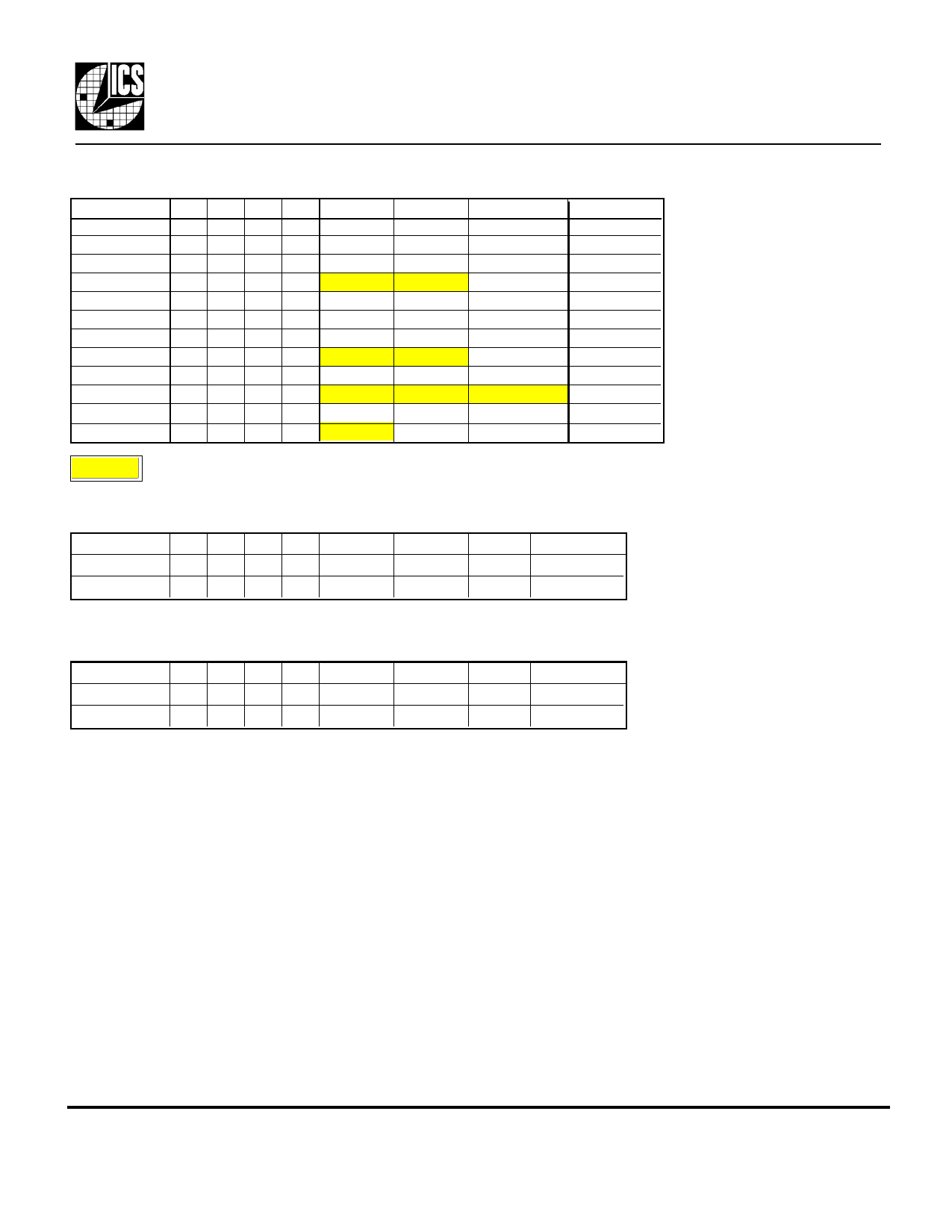

MK2049-03 Output Decoding Table – External Mode (MHz)

ICLK

8 kHz

8 kHz

8 kHz

8 kHz

8 kHz

8 kHz

8 kHz

8 kHz

8 kHz

8 kHz

8 kHz

8 kHz

FS3 FS2 FS1 FS0

0000

0001

0010

0011

0100

0101

0110

0111

1010

1011

1100

1101

CLK1

1.544

2.048

18.688

7.68

19.44

16.384

24.576

8.64

12.416

18.528

10.24

4.096

CLK2

3.088

4.096

37.376

15.36

38.88

32.768

49.152

17.28

24.832

37.056

20.48

8.192

CLK3

8 kHz

8 kHz

8 kHz

8 kHz

8 kHz

8 kHz

8 kHz

8 kHz

8 kHz

1.544 MHz

8 kHz

8 kHz

Crystal

12.352

12.288

9.344

10.24

9.72

8.192

12.288

11.52

12.416

12.352

10.24

8.192

= No Zero (Fixed) I/O Delay for these selections shown in the shaded boxes.

MK2049-03 Output Decoding Table – Loop Timing Mode (MHz) for T1/E1

ICLK

1.544

2.048

FS3 FS2 FS1 FS0

1000

1001

CLK1

1.544

2.048

CLK2

3.088

4.096

Crystal

12.352

12.288

CLK3

N/A

N/A

MK2049-03 Output Decoding Table – Buffer Mode (MHz)

ICLK

19 - 28

10 - 14

FS3 FS2 FS1 FS0

1110

1111

CLK1

ICLK/2

2*ICLK

CLK2 Crystal

ICLK ICLK/2

4*ICLK ICLK

• 0 = connect directly to ground, 1 = connect directly to VDD.

• Crystal is connected to pins 2 and 3; clock input is applied to pin 13.

CLK3

N/A

Low

OPERATING MODES

The MK2049-02/03 have three operating modes: External, Loop Timing, and Buffer. Although each

mode uses an input clock to generate various output clocks, there are important differences in their input

and crystal requirements.

External Mode

The MK2049-02/03 accept an external 8 kHz clock and will produce a number of common communica-

tion clock frequencies. The 8 kHz input clock does not need to have a 50% duty cycle; a “high” or “on”

pulse as narrow as 10 ns is acceptable. In the MK2049-02, the rising edge of CLK2 is aligned with the

rising edge of the 8 kHz ICLK; refer to Figure 1 for more details. In the MK2049-03, the rising edges of

CLK1 and CLK2 are both aligned with the rising edge of the 8 kHz ICLK (unless noted in the shaded area

of the table); refer to Figure 2 for more details.

MDS 2049-02/03 B

5

Revision 040601

Integrated Circuit Systems, Inc. • 525 Race Street • San Jose • CA • 95126 • (408)295-9800tel• www.icst.com

5 Page

MK2049-02/03

Communications Clock PLLs

LAYOUT AND EXTERNAL COMPONENTS (continued)

Determining the Crystal Frequency Adjustment Capacitors

To determine the crystal adjustment capacitor values, you will need a PC board of your final layout, a

frequency counter capable of less than 1 ppm resolution and accuracy, two power supplies, and some samples

of the crystals which you plan to use in production, along with measured initial accuracy for each crystal at

the specified load capacitance, CL .

To determine the value of the crystal capacitors:

1. Connect VDD of the MK2049 to 5.0 V. Connect pin 18 of the MK2049 to the second power supply.

Adjust the voltage on pin 18 to 0.0 V. Measure and record the frequency of the CLK1 or CLK2 output .

2. Adjust the voltage on pin 18 to 3.0 V. Measure and record the frequency of the same output.

To calculate the centering error:

Centering

error

= 106

(f3.0V - ftarget) + (f0.0V - ftarget)

ftarget

- errorxtal

Where ftarget = 44.736000 MHz, for example, and errorxtal = actual initial accuracy (in ppm) of the

crystal being measured.

If the centering error is less than ±15 ppm, no adjustment is needed. If the centering error is more than

15 ppm negative, the PC board has too much stray capacitance and will need to be redone with a new layout

to reduce stray capacitance. (The crystal may be re-specified to a lower load capacitance instead. Contact ICS

MicroClock for details.) If the centering error is more than 15 ppm positive, add identical fixed centering

capacitors from each crystal pin to ground. The value for each of these caps (in pF) is given by:

External Capacitor = 2*(centering error)/(trim sensitivity)

Trim sensitivity is a parameter which can be supplied by your crystal vendor. If you do not know the value,

assume it is 30 ppm/pF. After any changes, repeat the measurement to verify that the remaining error is

acceptably low (less than ±15 ppm).

The MicroClock Applications department can perform this procedure on your board. Call us at 408-295-

9800, and we will arrange for you to send us a PC board (stuffed or unstuffed) and one of your crystals. We

will calculate the value of capacitors needed.

MDS 2049-02/03 B

11

Revision 040601

Integrated Circuit Systems, Inc. • 525 Race Street • San Jose • CA • 95126 • (408)295-9800tel• www.icst.com

11 Page | ||

| Páginas | Total 12 Páginas | |

| PDF Descargar | [ Datasheet MK2049-02.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| MK2049-01 | Communications Clock PLL | Integrated Circuit Systems |

| MK2049-02 | Communications Clock PLLs | Integrated Circuit Systems |

| MK2049-03 | Communications Clock PLLs | Integrated Circuit Systems |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |