|

|

PDF W3100A Data sheet ( Hoja de datos )

| Número de pieza | W3100A | |

| Descripción | i2Chip W3100A | |

| Fabricantes | ETC | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de W3100A (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

www.i2Chip.com

i2Chip W3100A

Technical Datasheet v1.1

Description

The i2Chip W3100A is an LSI of hardware

protocol stack that provides an easy, low-cost solution

for highD-sepseecdrIinptetrinoent connectivity for digital devices

by allowFienag tsuimrpelse installation of TCP/IP stack in the

hardwaBre.lock Diagram

G

The W3100A offers system designers a quick,

easy way to add Ethernet networking functionality to

any product. Implementing this LSI into a system

can completely offload Internet connectivity and

processing standard protocols from the system,

thereby significantly reducing the software

development cost.

The W3100A contains TCP/IP Protocol Stacks

such as TCP, UDP, IP, ARP and ICMP protocols, as

well as Ethernet protocols such as Data Link Control

and MAC protocol.

The W3100A offers a socket API (Application

Programming Interface) that is similar to the windows

socket API. The chip offers Intel and Motorola

MCU (8051, i386, 6811 tested) bus interface and I2C

for upper-layer and supports standard MII interface for

under-layer Ethernet.

The W3100A can be applied to handheld devices

including Internet phones, VoIP SOC chips, Internet

MP3 players, handheld medical devices, LAN cards

for Web servers, cellular phones and many other non-

portable electronic devices such as large consumer

electronic products.G

Features

G

6/Hardware Internet protocols included:

TCP, IP Ver.4, UDP, ICMP, ARP

6/Hardware Ethernet protocols included:

DLC, MAC

6/Supports 4 independent connections simultaneously

6/Internal ICMP responds to PING commands

6/Protocol processing speed: full-duplex 4~5 Mbps

6/Intel/Motorola MCU bus Interface

6/I2C Interface

6/Standard MII Interface for under-layer physical chip

6/Socket API support for easy application programming

6/Supports full-duplex mode

6/Internal 16Kbytes Dual-port SRAM for data buffer

6/0.35 µm CMOS technology

6/Wide operating voltage:

3.3V internal operation, 5V tolerant 3.3V IOs

6/Small 64 Pin LQFP Package

Block Diagram

MODE0

MODE1

MODE2

/CS

/WR

/RD

/INT

ADDR(14:0)

DATA(7:0)

SCL

SDA

Protocol Engine

ICMP

TCP

IP

DLC

MAC

UDP

ARP

CLOCK

EX T_CL K

RESET

MII Interface

~pGGyhwpkGOyGhTGpGw GkPH/

:

1 page

62 /WR I WRITE ENABLE: This signal is active low.

63 /RD I READ ENABLE: This signal is active low.

59 SCL I SCL: clock used by I2C when using I2C Interface mode

External Pull high (4.7 kΩ) is required.

60

SDA

I/O SDA: data used by I2C when using I2C Interface mode

External Pull high (4.7 kΩ) is required.

Table 3: W3100A Miscellaneous Signal Description

PIN#

Signal I/O

Description

1

RESET

I RESET: Active High input that initializes or reinitializes the W3100A.

Asserting this pin will force a reset process to occur which will result

in all internal registers reinitializing to their default states as

specified for each bit in section x.x, and all strapping options are

reinitialized. Refer to section x.x for further detail regarding reset.

4

CLOCK

I CLOCK: primary clock required for internal operation of W3100A.

In general, PHY driving clock is shared for saving cost.

(25MHz is recommended)

Note) Sharing crystal source clock with multiple devices may cause

some troubles. In our reference design, we used Realtek's PHY and

one crystal for both PHY and W3100A with verification.

But for other kind of PHY, please confirm safety prior to decision.

33 EXT_CLK I EXTERNAL CLOCK: supplementary clock used for MCU I/F of

W3100A.

In external clocked mode, W3100A uses this clock to interface with

MCU, and the access time of W3100A varies upon the frequency of

the external clock. Refer to xx for detailed timing diagram.

Frequency higher than 25MHz clock rate is granted.

36

/LINK

I LINK: This is the signal generated by Ethernet PHY to indicate the

PHY is connected to the Ethernet HUB device or other peer device.

This is active low. W3100A can knows the status of physical line

connection with this /LINK input. If /LINK is high, W3100A interprets

the physical line is disconnected. It results in TCP timeout and

connection close.

In special PHY case, LINK signal varies in time, which can be

grounded.

35 /SERIAL I 10BASE-T SERIAL/NIBBLE SELECT: With the selection of this

active low input, transmit and receive data are exchanged serially at

a 10 MHz clock rate on the least significant bits of the nibble-wide

MII data buses, pins TXD[0] and RXD[0], respectively. This mode is

intended for use with the W3100A connected to a PHY using a 10

Mb/s serial interface.

There is an internal pull-up resister for this pin. If this pin is left

floated externally, then the device will be configured to normal

mode. This pin must be externally pulled low (typically x kΩ) in

~pGGyhwpkGOyGhTGpGw GkPHG

\

5 Page

Register Definitions.

Register sets are categorized into (i) control registers related to command, status and interrupt, (ii) system

registers for gateway address, subnet mask, source IP, source HA (Hardware Address) and timeout value, (iii)

pointer registers for managing to send, receive data, and (iv) channel registers that control operation of each

channel. R/W access to reserved register is not allowed, and also, writing on read-only register is not

allowed.

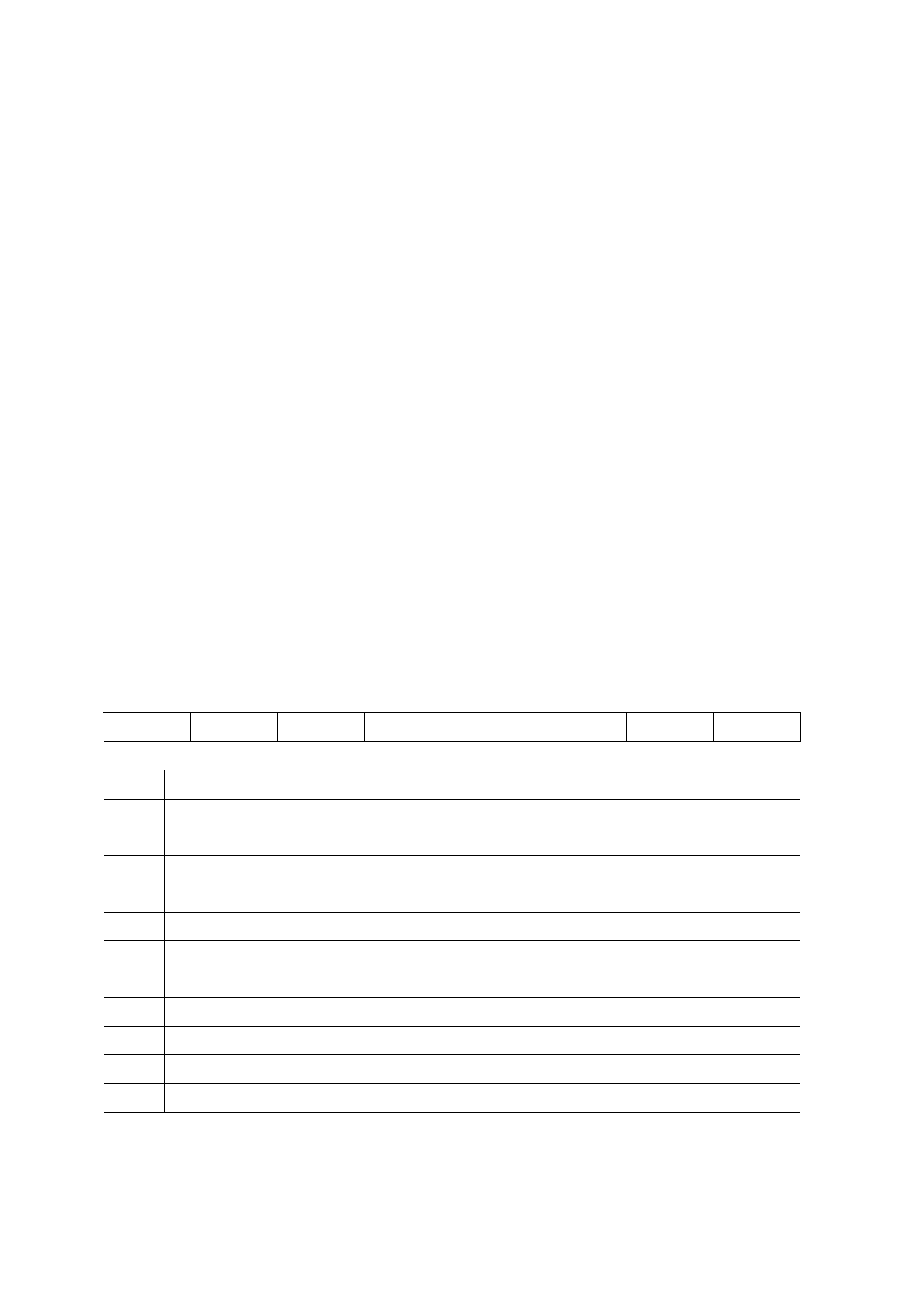

1. Control Registers

C0_CR (Channel 0 Command Register) [R/W, 0x00]

This register commands Channel 0 socket to initialize, connect, close, transmit and receive data. Sys_Init

command is used to set the gateway, subnet mask, source IP and source H/W Address. The same command is

used to close the socket in all channels.

Sock_Init, Connect, Listen, Close, Send and Recv are used when initializing, establishing a connection,

terminating a connection, sending and receiving data for Channel 0 socket. Each corresponding bit is

automatically cleared after executing the command.

Sock_Init command opens the corresponding Channel in TCP, UDP, RAW mode according to the protocol

value as set at C0_SOPR (Channel 0 Socket Option Protocol Register).

MCU can initialize the internal setting value of the chip by using S/W Reset.

Each bit in this register is automatically cleared after executing the command.

7

S/W Reset

6

Recv

5

Send

4

Close

3

Listen

2

Connect

1

Sock_Init

0

Sys_Init

Bit

D0

D1

D2

D3

D4

D5

D6

D7

Symbol

Description

Sys_Init Command to set Gateway IP Address, Subnet Mask, Source H/W Address,

Source IP Address

Sock_Init Command to set corresponding protocol at C0_SOPR and open Channel 0

socket

Connect Command for Channel 0 socket to make a connection to the server

Listen

Command to stand by for connection when Channel 0 socket acts in server

mode

Close

Command to terminate connection and close Channel 0 socket

Send

Command to transmit Channel 0 socket data

Recv

Command to receive Channel 0 socket data

S/W Reset S/W Reset command

oGpGj G~¡GO~pSGpUPG

XX

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet W3100A.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| W3100A | i2Chip W3100A | ETC |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |