|

|

PDF FDG6318PZ Data sheet ( Hoja de datos )

| Número de pieza | FDG6318PZ | |

| Descripción | Dual P-Channel/ Digital FET | |

| Fabricantes | Fairchild Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de FDG6318PZ (archivo pdf) en la parte inferior de esta página. Total 9 Páginas | ||

|

No Preview Available !

January 2003

FDG6318PZ

Dual P-Channel, Digital FET

General Description

These dual P-Channel logic level enhancement mode

MOSFET are produced using Fairchild Semiconductor’s

especially tailored to minimize on-state resistance. This

device has been designed especially for bipolar digital

transistors and small signal MOSFETS

Applications

• Battery management

Features

• -0.5A, -20V. rDS(ON) = 780mΩ (Max)@ VGS = -4.5 V

rDS(ON) = 1200mΩ (Max) @ VGS = -2.5 V

• Very low level gate drive requirements allowing direct

operation in 3V circuits (VGS(TH) < 1.5V).

• Gate-Source Zener for ESD ruggedness (>1.4kV Human

Body Model).

• Compact industry standard SC-70-6 surface mount

package.

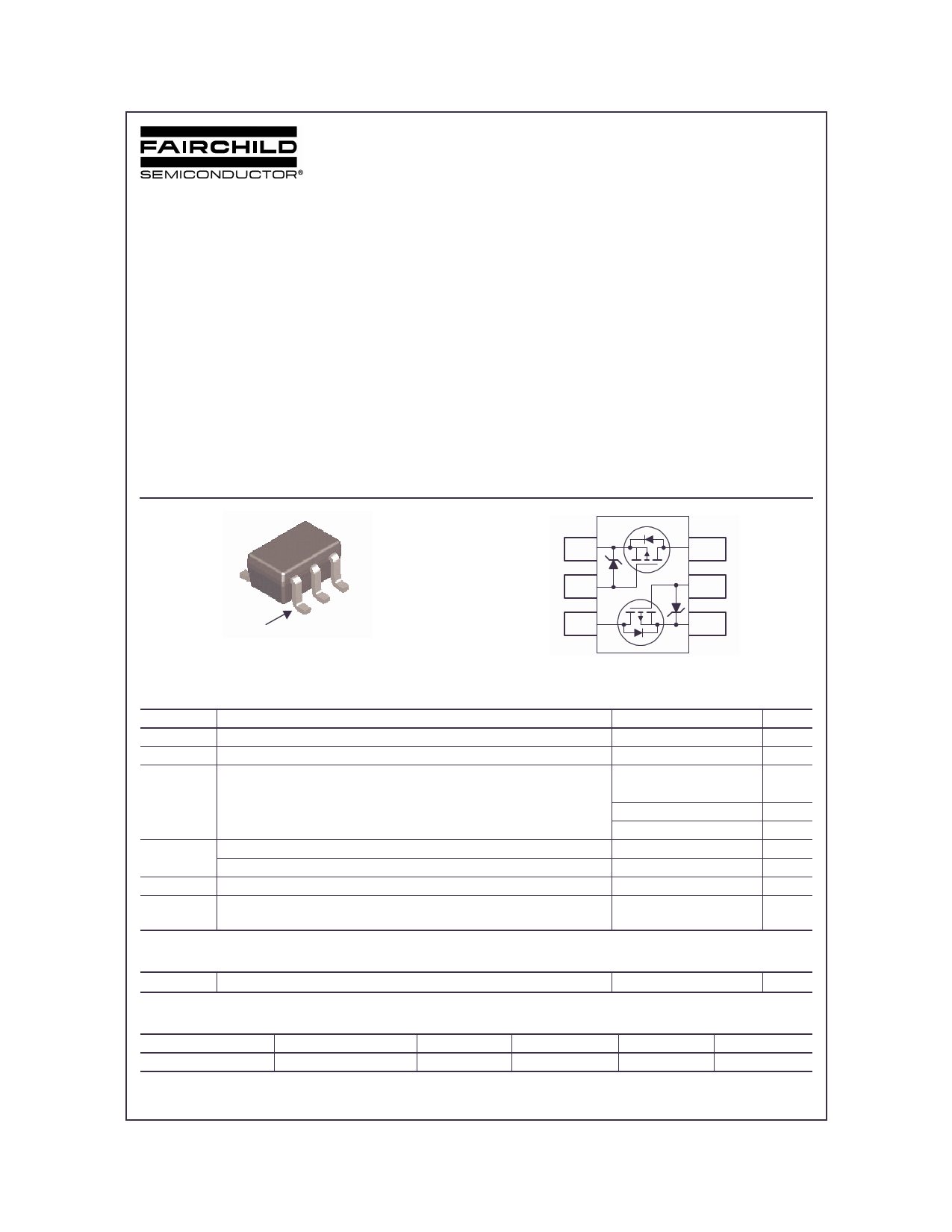

S

G

D

S 1 or 4

6 or 3 D

Pin 1

D

G

S

G 2 or 5

D 3 or 6

5 or 2 G

4 or 1 S

SC70-6

The pinouts are symmetrical; pin1 and pin 4 are interchangeable.

MOSFET Maximum Ratings TA=25°C unless otherwise noted

Symbol

VDSS

VGS

ID

Parameter

Drain to Source Voltage

Gate to Source Voltage

Drain Current

Continuous (TC = 25oC, VGS = - 4.5V)

Continuous (TC = 100oC, VGS = - 2.5V)

Pulsed

Ratings

-20

±12

-0.5

-0.3

Figure 4

PD Power dissipation

Derate above 25°C

0.3

2.4

TJ, TSTG

ESD

Operating and Storage Temperature

Electrostatic Discharge Rating MIL-STD-883D

Human Body Model ( 100pF / 1500Ω )

-55 to 150

1.4

Units

V

V

A

A

W

mW/oC

oC

kV

Thermal Characteristics

RθJA

Thermal Resistance Junction to Ambient (Note 1)

Package Marking and Ordering Information

Device Marking

.68

Device

FDG6318PZ

Package

SC70-6

Reel Size

7”

415

Tape Width

8 mm

oC/W

Quantity

3000

©2003 Fairchild Semiconductor Corporation

FDG6318PZ Rev. B

1 page

Typical Characteristic (Continued) TA = 25°C unless otherwise noted

1.10

ID = 250µA

1.05

200

CISS = CGS + CGD

100

COSS ≅ CDS + CGD

1.00

0.95

-80

-40 0

40 80 120

TJ, JUNCTION TEMPERATURE (oC)

160

Figure 11. Normalized Drain to Source

Breakdown Voltage vs Junction Temperature

CRSS = CGD

10

VGS = 0V, f = 1MHz

5

0.1 1

10

-VDS , DRAIN TO SOURCE VOLTAGE (V)

20

Figure 12. Capacitance vs Drain to Source

Voltage

10

VDD = -10V

8

6

4

2

0

0

WAVEFORMS IN

DESCENDING ORDER:

ID = -0.5A

ID = -0.1A

0.5 1.0 1.5

Qg, GATE CHARGE (nC)

2.0

Figure 13. Gate Charge Waveforms for Constant Gate Currents

©2003 Fairchild Semiconductor Corporation

FDG6318PZ Rev. B

5 Page | ||

| Páginas | Total 9 Páginas | |

| PDF Descargar | [ Datasheet FDG6318PZ.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| FDG6318P | Dual P-Channel/ Digital FET | Fairchild Semiconductor |

| FDG6318PZ | Dual P-Channel/ Digital FET | Fairchild Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |