|

|

PDF AD5011 Data sheet ( Hoja de datos )

| Número de pieza | AD5011 | |

| Descripción | 2 Pair/1 Pair ETSI Compatible HDSL Analog Front End | |

| Fabricantes | Analog Devices | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de AD5011 (archivo pdf) en la parte inferior de esta página. Total 8 Páginas | ||

|

No Preview Available !

PRELIMINARY TECHNICAL DATA

a

2Pair/1 PairETSICompatible

HDSL Analog Front End

Preliminary Technical Data

AD5011

FEATURES

Integrated front End for Single Pair or Two Pair HDSL

Systems

Meets ETSI Specifications

Supports 1168 kbps and 2.32 Mbps

Programmable Filtering Supports Adaptive HDSL

Transmit and Receive Signal Path Functions

Receive Hybrid Amplifier, PGA, ADC and Adaptable

Filter

Transmit DAC, Adaptable Filter and Differential

Outputs

Normal Loopback

Serial Interface to Digital Transceivers

Single 3 V Power Supply

GENERAL DESCRIPTION

The AD5011 is an analog front end for two pair or single

pair HDSL applications that use 1168 kbps or 2.32 Mbps

data rates. The device integrates all the transmit and receive

functional blocks. A standard serial interface is used to

communicate with the DAC and ADC. The filters in both

the transmit and receive paths are programmable which

allows adaptive HDSL to be performed also. The part is

available in a 48-pin LQFP package and is specified for a

temperature range of -40 oC to +85 oC.

FUNCTIONAL BLOCK DIAGRAM

V D R IV E

TxDATA

TxSYNC

TxCLK

T x-D E C O U P

14-Bit DAC

ADCCLK

SCLK

SDO

DR

CAP-T

CAP-B

R E F -C O M

VREF

CM-LVL

12-Bit ADC

ADC

B u ffe r

S P IC L K

TFS

DT

DR

RESETB

PW RDOWNB

C o n tro l/

SPI Configuration

6 P ole A da ptive

Bessel Filter

PGA

0 dB

-6 dB

L in e

D river

4 P ole A da ptive

Butterworth Filter

PGA

H yb rid

-6 dB

-3 dB

0 dB

+3 dB

+6 dB

DRV-OUTP

DRV-OUTN

H Y B IN -2 B

H Y B IN -2 A

H Y B IN -1 A

H Y B IN -1 B

REV PrA

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700

Fax: 781/326-8703

World Wide Web Site: hppt://www.analog.com

1 page

PRELIMINARY TECHNICAL DATA

AD5011

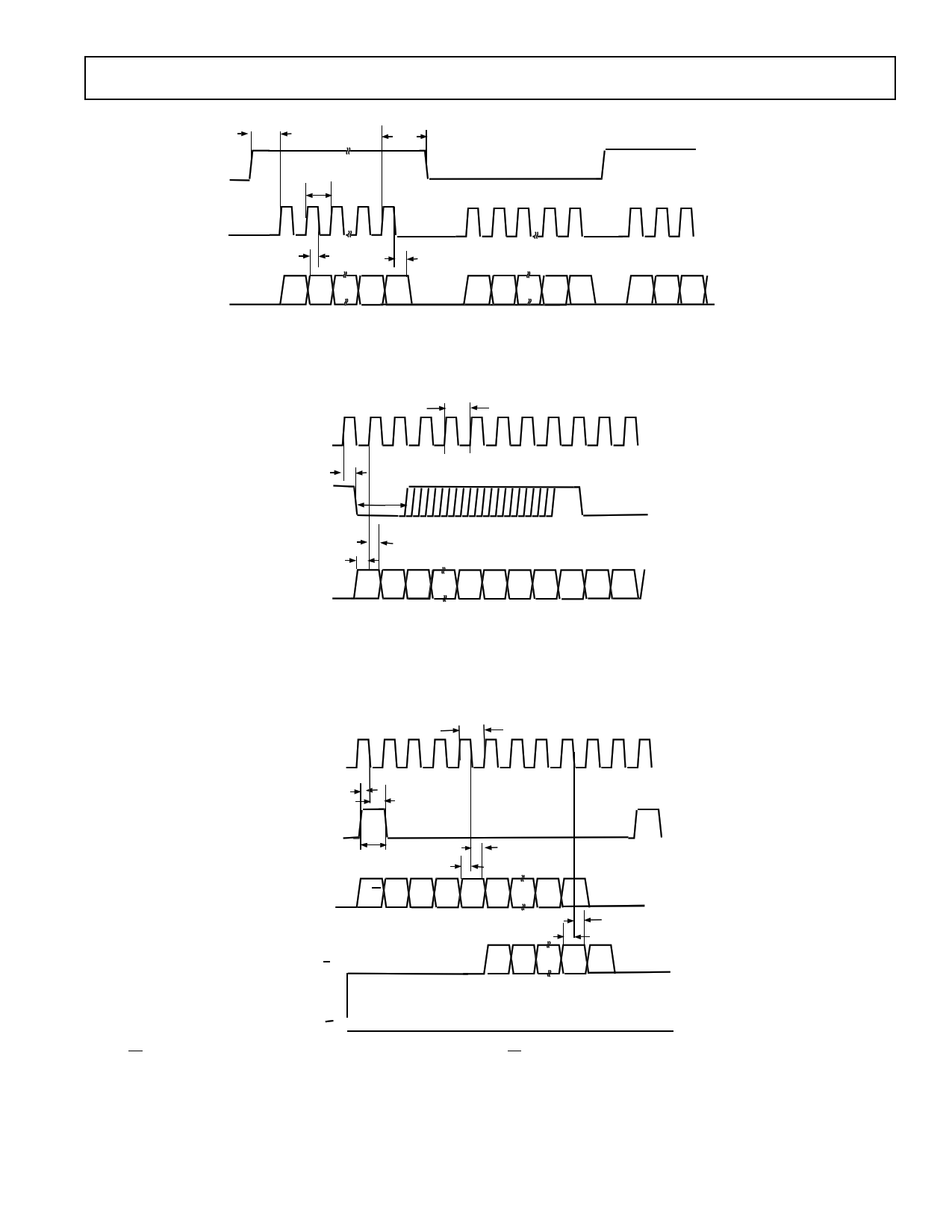

ADCCLK

t6

t8

t7

SCLK

SDO

t9

D11 D10

t 10

D1 D0

D11 D10

D1 D0

D11 D10 D9

SCLK activity and serial output data activity does not coincide with the sesitive ADCCLK clock edges

Figure 2. ADC Timing (1160 kHz < ADCCLK <= 2320 kHz)

TxCLK

t 15

t 14

TxSYNC

t 13

t 11

TxDATA

t 12

D13 D12 D11

D2 D1 D0 X

X D13 D12

The rising edge of TxSYNC can occur anywhere as long at the TxSYNC low time exceeds one TxCLK period. The TxSYNC falling edge

must occur after the TxCLK rising edge which captures the LSB of the previous word. This ensures correct loading into the DAC. The

first 14 bits are loaded into the DAC, the 2 LSBs being don't cares.

Figure 3. DAC Timing

SPICLK

t 16

t 17

t 18

TFS

t 19

t 21

t 20

DT R/W SEL2 SEL1 SEL0 D11 D10

D1 DO

DR

(R/W = 1)

t 23

t 22

D11 D10

D1 DO

DR

(R/W = 0

If R/W = 1, the selected register's contents will be output on DR. If R/W = 0, no data will be output on DR. The SEL bits identify

which of the four register banks is being written to. The 12 LSBs contain the word. When the AD5011 is reset using RESETB, the

registers are reset to zero.

Figure 4. Control Interface

REV PrA

–5–

5 Page | ||

| Páginas | Total 8 Páginas | |

| PDF Descargar | [ Datasheet AD5011.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| AD5011 | 2 Pair/1 Pair ETSI Compatible HDSL Analog Front End | Analog Devices |

| AD5012N2L | AC-DC / External Freestanding Adapter | Emerson |

| AD5012N2LM | AC-DC / External Freestanding Medical Adapter | Emerson |

| AD5012N3L | AC-DC / External Freestanding Adapter | Emerson |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |