|

|

PDF AD660 Data sheet ( Hoja de datos )

| Número de pieza | AD660 | |

| Descripción | Monolithic 16-Bit Serial/Byte DACPORT | |

| Fabricantes | Analog Devices | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de AD660 (archivo pdf) en la parte inferior de esta página. Total 12 Páginas | ||

|

No Preview Available !

a

Monolithic 16-Bit

Serial/Byte DACPORT

AD660

FEATURES

Complete 16-Bit D/A Function

On-Chip Output Amplifier

On-Chip Buried Zener Voltage Reference

؎1 LSB Integral Linearity

15-Bit Monotonic over Temperature

Microprocessor Compatible

Serial or Byte Input

Double Buffered Latches

Fast (40 ns) Write Pulse

Asynchronous Clear (to 0 V) Function

Serial Output Pin Facilitates Daisy Chaining

Unipolar or Bipolar Output

Low Glitch: 15 nV-s

Low THD+N: 0.009%

FUNCTIONAL BLOCK DIAGRAM

UNI/BIP CLR/

LBE CS

15 14

SIN/ MSB/LSB/

DB0 DB1 DB7

12 11

5

HBE 16

SER 17

CLR 18

CONTROL

LOGIC

16-BIT LATCH

16-BIT LATCH

LDAC 19

REF IN 23

10k

16-BIT DAC

+10V REF

24 1 2

REF OUT –VEE +VCC

AD660

10k

10.05k

13 SOUT

22 SPAN/

BIP

OFFSET

21 VOUT

34

+VLL DGND

20 AGND

PRODUCT DESCRIPTION

The AD660 DACPORT® is a complete 16-bit monolithic D/A

converter with an on-board voltage reference, double buffered

latches and output amplifier. It is manufactured on Analog De-

vices’ BiMOS II process. This process allows the fabrication of

low power CMOS logic functions on the same chip as high pre-

cision bipolar linear circuitry.

The AD660’s architecture ensures 15-bit monotonicity over

time and temperature. Integral and differential nonlinearity is

maintained at ± 0.003% max. The on-chip output amplifier pro-

vides a voltage output settling time of 10 µs to within 1/2 LSB

for a full-scale step.

The AD660 has an extremely flexible digital interface. Data can

be loaded into the AD660 in serial mode or as two 8-bit bytes.

This is made possible by two digital input pins which have dual

functions. The serial mode input format is pin selectable to be

MSB or LSB first. The serial output pin allows the user to daisy

chain several AD660s by shifting the data through the input

latch into the next DAC thus minimizing the number of control

lines required to SIN, CS and LDAC. The byte mode input for-

mat is also flexible in that the high byte or low byte data can be

loaded first. The double buffered latch structure eliminates data

skew errors and provides for simultaneous updating of DACs in

a multi-DAC system.

The AD660 is available in five grades. AN and BN versions are

specified from –40°C to +85°C and are packaged in a 24-pin

300 mil plastic DIP. AR and BR versions are also specified from

–40°C to +85°C and are packaged in a 24-pin SOIC. The SQ

version is packaged in a 24-pin 300 mil cerdip package and is

also available compliant to MIL-STD-883. Refer to the AD660/

883B data sheet for specifications and test conditions.

PRODUCT HIGHLIGHTS

1. The AD660 is a complete 16-bit DAC, with a voltage refer-

ence, double buffered latches and output amplifier on a sin-

gle chip.

2. The internal buried Zener reference is laser trimmed to

10.000 volts with a ± 0.1% maximum error and a tempera-

ture drift performance of ± 15 ppm/°C. The reference is

available for external applications.

3. The output range of the AD660 is pin programmable and can

be set to provide a unipolar output range of 0 V to +10 V or

a bipolar output range of –10 V to +10 V. No external com-

ponents are required.

4. The AD660 is both dc and ac specified. DC specifications

include ± 1 LSB INL and ± 1 LSB DNL errors. AC specifi-

cations include 0.009% THD+N and 83 dB SNR.

5. The double buffered latches on the AD660 eliminate data

skew errors and allow simultaneous updating of DACs in

multi-DAC applications.

6. The CLEAR function can asynchronously set the output to

0 V regardless of whether the DAC is in unipolar or bipolar

mode.

7. The output amplifier settles within 10 µs to ± 1/2 LSB for a

full-scale step and within 2.5 µs for a 1 LSB step over tem-

perature. The output glitch is typically 15 nV-s when a full-

scale step is loaded.

DACPORT is a registered trademark of Analog Devices, Inc.

REV. A

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 617/329-4700

Fax: 617/326-8703

1 page

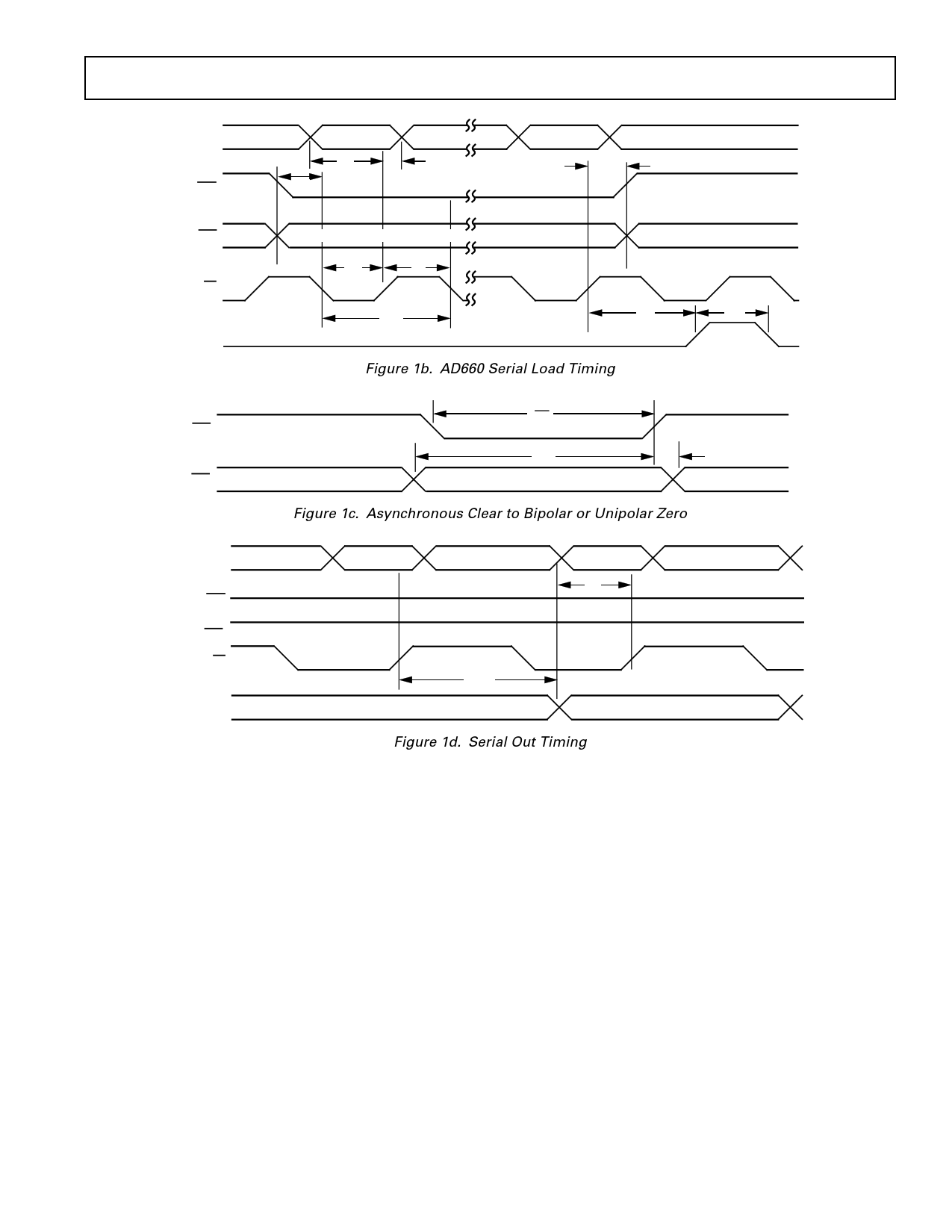

AD660

BIT0

SER

VALID 1

tDS

tSS

tDH

VALID 16

tSH

BIT1

CS

LDAC

CLR

LBE

"1" = MSB FIRST, "0" = LSB FIRST

tLO tHI

tCLK

tLH tLW

Figure 1b. AD660 Serial Load Timing

tCLR

tSET

"1" = BIP 0, "0" = UNI 0

tHOLD

Figure 1c. Asynchronous Clear to Bipolar or Unipolar Zero

BIT0

SER

BIT 1

(MSB/LSB)

CS

SERIAL

OUT

VALID 16

VALID 17

tDS

tPROP

VALID SOUT1

Figure 1d. Serial Out Timing

DEFINITIONS OF SPECIFICATIONS

INTEGRAL NONLINEARITY: Analog Devices defines

integral nonlinearity as the maximum deviation of the actual,

adjusted DAC output from the ideal analog output (a straight

line drawn from 0 to FS–1 LSB) for any bit combination. This

is also referred to as relative accuracy.

DIFFERENTIAL NONLINEARITY: Differential nonlinearity

is the measure of the change in the analog output, normalized to

full scale, associated with a 1 LSB change in the digital input

code. Monotonic behavior requires that the differential linearity

error be greater than or equal to –1 LSB over the temperature

range of interest.

MONOTONICITY: A DAC is monotonic if the output either

increases or remains constant for increasing digital inputs with

the result that the output will always be a single-valued function

of the input.

GAIN ERROR: Gain error is a measure of the output error be-

tween an ideal DAC and the actual device output with all 1s

loaded after offset error has been adjusted out.

OFFSET ERROR: Offset error is a combination of the offset

errors of the voltage-mode DAC and the output amplifier and is

measured with all 0s loaded in the DAC.

BIPOLAR ZERO ERROR: When the AD660 is connected for

bipolar output and 10 . . . 000 is loaded in the DAC, the devia-

tion of the analog output from the ideal midscale value of 0 V is

called the bipolar zero error.

DRIFT: Drift is the change in a parameter (such as gain, offset

and bipolar zero) over a specified temperature range. The drift

temperature coefficient, specified in ppm/°C, is calculated by

measuring the parameter at TMIN, 25°C and TMAX and dividing

the change in the parameter by the corresponding temperature

change.

TOTAL HARMONIC DISTORTION + NOISE: Total har-

monic distortion + noise (THD+N) is defined as the ratio of the

square root of the sum of the squares of the values of the har-

monics and noise to the value of the fundamental input fre-

quency. It is usually expressed in percent (%).

THD+N is a measure of the magnitude and distribution of lin-

earity error, differential linearity error, quantization error and

noise. The distribution of these errors may be different, depend-

ing upon the amplitude of the output signal. Therefore, to be

the most useful, THD+N should be specified for both large and

small signal amplitudes.

REV. A

–5–

5 Page

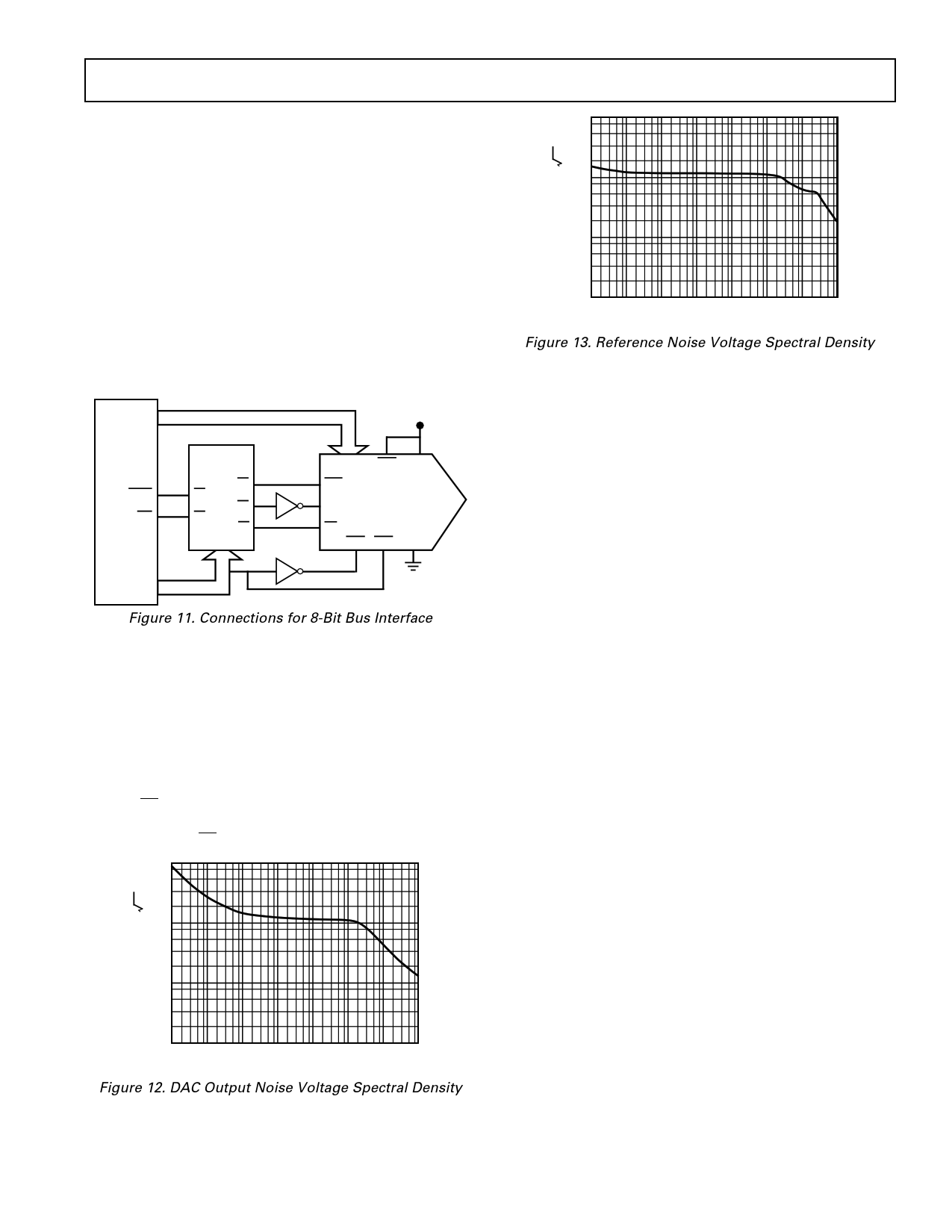

Applications Information–AD660

The address decoder analyzes the input-output address pro-

duced by the processor to select the function to be performed by

the AD660, qualified by the coincidence of the Input-Output

Request (IORQ*) and Write (WR*) pins. The least significant

address bit (A0) determines if the low or high byte register of

the AD660 is active. More significant address bits select be-

tween input register loading, DAC output update, and unipolar

or bipolar clear.

A typical Z-80 software routine begins by writing the low byte of

the desired 16-bit DAC data to address 0, followed by the high

byte to address 1. The DAC output is then updated by activat-

ing LDAC with a write to address 2 (or 3). A clear to unipolar

zero occurs on a write to address 4, and a clear to bipolar zero is

performed by a write to address 5. The actual data written to

addresses 2 through 5 is irrelevant. The decoder can easily be

expanded to control as many AD660s as required.

D0-D7

+5V

IORQ

WR

Z80

A0-A15

ADDRESS

DECODE

Y2

E2

Y1

E1

Y0

A1–A15

A0

DB0-DB7 SER VLL

CLR

LDAC

AD660

CS

HBE LBE DGND

Figure 11. Connections for 8-Bit Bus Interface

NOISE

In high resolution systems, noise is often the limiting factor. A

16-bit DAC with a 10 volt span has an LSB size of 153 µV

(–96 dB). Therefore, the noise floor must remain below this

level in the frequency range of interest. The AD660’s noise

spectral density is shown in Figures 12 and 13. Figure 12 shows

the DAC output noise voltage spectral density for a 20 V span

excluding the reference. This figure shows the 1/f corner

frequency at 100 Hz and the wideband noise to be below

120 nV/√Hz. Figure 13 shows the reference noise voltage spec-

tral density. This figure shows the reference wideband noise to

be below 125 nV/√Hz.

1000

100

10

1

1 10 100 1k 10k 100k 1M 10M

FREQUENCY – Hz

Figure 12. DAC Output Noise Voltage Spectral Density

1000

100

10

1

1 10 100 1k 10k 100k 1M 10M

FREQUENCY – Hz

Figure 13. Reference Noise Voltage Spectral Density

BOARD LAYOUT

Designing with high resolution data converters requires careful

attention to board layout. Trace impedance is the first issue. A

306 µA current through a 0.5 Ω trace will develop a voltage

drop of 153 µV, which is 1 LSB at the 16-bit level for a 10 V

full-scale span. In addition to ground drops, inductive and

capacitive coupling need to be considered, especially when high

accuracy analog signals share the same board with digital sig-

nals. Finally, power supplies need to be decoupled in order to

filter out ac noise.

Analog and digital signals should not share a common path.

Each signal should have an appropriate analog or digital return

routed close to it. Using this approach, signal loops enclose a

small area, minimizing the inductive coupling of noise. Wide PC

tracks, large gauge wire, and ground planes are highly recom-

mended to provide low impedance signal paths. Separate analog

and digital ground planes should also be used, with a single in-

terconnection point to minimize ground loops. Analog signals

should be routed as far as possible from digital signals and

should cross them at right angles.

One feature that the AD660 incorporates to help the user layout

is that the analog pins (VCC, VEE, REF OUT, REF IN, SPAN/

BIP OFFSET, VOUT and AGND) are adjacent to help isolate

analog signals from digital signals.

SUPPLY DECOUPLING

The AD660 power supplies should be well filtered, well regu-

lated, and free from high frequency noise. Switching power sup-

plies are not recommended due to their tendency to generate

spikes which can induce noise in the analog system.

Decoupling capacitors should be used in very close layout prox-

imity between all power supply pins and ground. A 10 µF tanta-

lum capacitor in parallel with a 0.1 µF ceramic capacitor

provides adequate decoupling. VCC and VEE should be bypassed

to analog ground, while VLL should be decoupled to digital

ground.

An effort should be made to minimize the trace length between

the capacitor leads and the respective converter power supply

and common pins. The circuit layout should attempt to locate

the AD660, associated analog circuitry and interconnections as

far as possible from logic circuitry. A solid analog ground plane

around the AD660 will isolate large switching ground currents.

For these reasons, the use of wire wrap circuit construction

is not recommended; careful printed circuit construction is

preferred.

REV. A

–11–

11 Page | ||

| Páginas | Total 12 Páginas | |

| PDF Descargar | [ Datasheet AD660.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| AD660 | Monolithic 16-Bit Serial/Byte DACPORT | Analog Devices |

| AD6600 | Dual Channel/ Gain-Ranging ADC with RSSI | Analog Devices |

| AD6620 | 65 MSPS Digital Receive Signal Processor | Analog Devices |

| AD6622 | Four-Channel/ 75 MSPS Digital Transmit Signal Processor TSP | Analog Devices |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |