|

|

PDF AD9240 Data sheet ( Hoja de datos )

| Número de pieza | AD9240 | |

| Descripción | Monolithic A/D Converter | |

| Fabricantes | Analog Devices | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de AD9240 (archivo pdf) en la parte inferior de esta página. Total 25 Páginas | ||

|

No Preview Available !

a

FEATURES

Monolithic 14-Bit, 10 MSPS A/D Converter

Low Power Dissipation: 285 mW

Single +5 V Supply

Integral Nonlinearity Error: 2.5 LSB

Differential Nonlinearity Error: 0.6 LSB

Input Referred Noise: 0.36 LSB

Complete: On-Chip Sample-and-Hold Amplifier and

Voltage Reference

Signal-to-Noise and Distortion Ratio: 77.5 dB

Spurious-Free Dynamic Range: 90 dB

Out-of-Range Indicator

Straight Binary Output Data

44-Lead MQFP

Complete 14-Bit, 10 MSPS

Monolithic A/D Converter

AD9240

FUNCTIONAL BLOCK DIAGRAM

VINA

VINB

CML

CAPT

CAPB

VREF

SENSE

SHA

CLK

AVDD

DVDD DRVDD

MDAC1

GAIN = 16

5

A/D

5

MDAC2

GAIN = 8

MDAC3

GAIN = 8

4

A/D

4

A/D

44

DIGITAL CORRECTION LOGIC

14

OUTPUT BUFFERS

A/D

4

MODE

SELECT

1V

AD9240

REFCOM

AVSS

DVSS

DRVSS

BIAS

OTR

BIT 1

(MSB)

BIT 14

(LSB)

PRODUCT DESCRIPTION

The AD9240 is a 10 MSPS, single supply, 14-bit analog-to-

digital converter (ADC). It combines a low cost, high speed

CMOS process and a novel architecture to achieve the resolution

and speed of existing hybrid implementations at a fraction of the

power consumption and cost. It is a complete, monolithic ADC

with an on-chip, high performance, low noise sample-and-hold

amplifier and programmable voltage reference. An external refer-

ence can also be chosen to suit the dc accuracy and temperature

drift requirements of the application. The device uses a multistage

differential pipelined architecture with digital output error correc-

tion logic to guarantee no missing codes over the full operating

temperature range.

The input of the AD9240 is highly flexible, allowing for easy

interfacing to imaging, communications, medical and data-

acquisition systems. A truly differential input structure allows

for both single-ended and differential input interfaces of varying

input spans. The sample-and-hold amplifier (SHA) is equally

suited for multiplexed systems that switch full-scale voltage

levels in successive channels as well as sampling single-channel

inputs at frequencies up to and beyond the Nyquist rate. The

AD9240 also performs well in communication systems employ-

ing Direct-IF Down Conversion, since the SHA in the differen-

tial input mode can achieve excellent dynamic performance well

beyond its specified Nyquist frequency of 5 MHz.

A single clock input is used to control all internal conversion

cycles. The digital output data is presented in straight binary

output format. An out-of-range (OTR) signal indicates an

overflow condition which can be used with the most significant

bit to determine low or high overflow.

PRODUCT HIGHLIGHTS

The AD9240 offers a complete single-chip sampling 14-bit,

analog-to-digital conversion function in a 44-lead Metric Quad

Flatpack.

Low Power and Single Supply

The AD9240 consumes only 280 mW on a single +5 V power

supply.

Excellent DC Performance Over Temperature

The AD9240 provides no missing codes, and excellent tempera-

ture drift performance over the full operating temperature range.

Excellent AC Performance and Low Noise

The AD9240 provides nearly 13 ENOB performance and has an

input referred noise of 0.36 LSB rms.

Flexible Analog Input Range

The versatile onboard sample-and-hold (SHA) can be configured

for either single ended or differential inputs of varying input spans.

Flexible Digital Outputs

The digital outputs can be configured to interface with +3 V and

+5 V CMOS logic families.

Excellent Undersampling Performance

The full power bandwidth and dynamic range of the AD9240

make it well suited for Direct-IF Down Conversion extending to

45 MHz.

REV.B

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 World Wide Web Site: http://www.analog.com

Fax: 781/461-3113

© Analog Devices, Inc., 2010

1 page

AD9240

SWITCHING SPECIFICATIONS (TMIN to TMAX with AVDD = +5 V, DVDD = +5 V, DRVDD = +5 V, RBIAS = 2 k⍀, CL = 20 pF)

Parameters

Symbol

AD9240

Units

Clock Period1

CLOCK Pulsewidth High

CLOCK Pulsewidth Low

Output Delay

Pipeline Delay (Latency)

tC

tCH

tCL

tOD

100 ns min

45 ns min

45 ns min

8 ns min

13 ns typ

19 ns max

3 Clock Cycles

NOTES

1The clock period may be extended to 1 ms without degradation in specified performance @ +25 °C.

Specifications subject to change without notice.

S1 S2

ANALOG

INPUT

tC

tCH tCL

S4

S3

INPUT

CLOCK

tOD

THERMAL CHARACTERISTICS

Thermal Resistance

44-Lead MQFP

θJA = 53.2°C/W

θJC = 19°C/W

DATA

OUTPUT

DATA 1

Figure 1. Timing Diagram

ABSOLUTE MAXIMUM RATINGS*

Parameter

With

Respect

to Min

Max

Units

AVDD

DVDD

AVSS

AVDD

DRVDD

DRVSS

REFCOM

CLK

Digital Outputs

VINA, VINB

VREF

SENSE

CAPB, CAPT

BIAS

Junction Temperature

Storage Temperature

Lead Temperature

(10 sec)

AVSS

DVSS

DVSS

DVDD

DRVSS

AVSS

AVSS

AVSS

DRVSS

AVSS

AVSS

AVSS

AVSS

AVSS

–0.3 +6.5

V

–0.3 +6.5

V

–0.3 +0.3

V

–6.5 +6.5

V

–0.3 +6.5

V

–0.3 +0.3

V

–0.3 +0.3

V

–0.3 AVDD + 0.3 V

–0.3 DRVDD + 0.3 V

–0.3 AVDD + 0.3 V

–0.3 AVDD + 0.3 V

–0.3 AVDD + 0.3 V

–0.3 AVDD + 0.3 V

–0.3 AVDD + 0.3 V

+150

°C

–65 +150

°C

+300

°C

*Stresses above those listed under Absolute Maximum Ratings may cause perma-

nent damage to the device. This is a stress rating only; functional operation of the

device at these or any other conditions above those indicated in the operational

sections of this specification is not implied. Exposure to absolute maximum ratings

for extended periods may effect device reliability.

PIN CONFIGURATION

44 43 42 41 40 39 38 37 36 35 34

DVSS 1

AVSS 2

DVDD 3

AVDD 4

DRVSS 5

DRVDD 6

CLK 7

NC 8

NC 9

NC 10

(LSB) BIT 14 11

PIN 1

IDENTIFIER

AD9240

TOP VIEW

(Not to Scale)

33 REFCOM

32 VREF

31 SENSE

30 NC

29 AVSS

28 AVDD

27 NC

26 NC

25 OTR

24 BIT 1 (MSB)

23 BIT 2

12 13 14 15 16 17 18 19 20 21 22

NC = NO CONNECT

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection.

Although the AD9240 features proprietary ESD protection circuitry, permanent damage may

occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD

precautions are recommended to avoid performance degradation or loss of functionality.

WARNING!

ESD SENSITIVE DEVICE

–4– REV.B

5 Page

AD9240

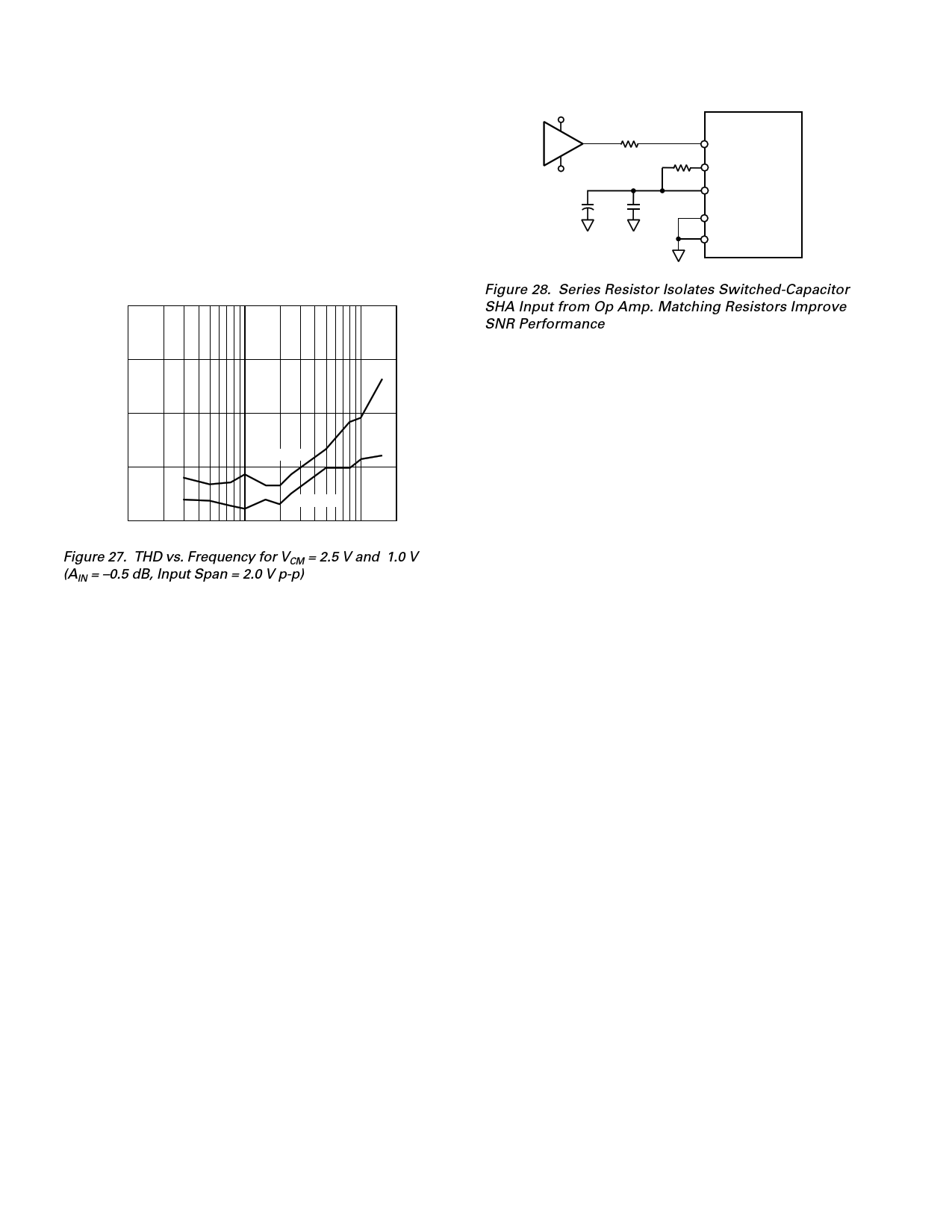

Figure 27 compares the AD9240’s THD vs. frequency perfor-

mance for a 2 V input span with a common-mode voltage of

1 V and 2.5 V. Note the difference in the amount of degrada-

tion in THD performance as the input frequency increases.

Similarly, note how the THD performance at lower frequencies

becomes less sensitive to the common-mode voltage. As the

input frequency approaches dc, the distortion will be domi-

nated by static nonlinearities such as INL and DNL. It is

important to note that these dc static nonlinearities are inde-

pendent of any RON modulation.

–50

–60

–70

VCM = 1.0V

–80

VCM = 2.5V

–90

0.1

1

FREQUENCY – MHz

10 20

Figure 27. THD vs. Frequency for VCM = 2.5 V and 1.0 V

(AIN = –0.5 dB, Input Span = 2.0 V p-p)

Due to the high degree of symmetry within the SHA topology, a

significant improvement in distortion performance for differen-

tial input signals with frequencies up to and beyond Nyquist can

be realized. This inherent symmetry provides excellent cancella-

tion of both common-mode distortion and noise. Also, the

required input signal voltage span is reduced a factor of two

which further reduces the degree of RON modulation and its

effects on distortion.

The optimum noise and dc linearity performance for either

differential or single-ended inputs is achieved with the largest

input signal voltage span (i.e., 5 V input span) and matched

input impedance for VINA and VINB. Note that only a slight

degradation in dc linearity performance exists between the

2 V and 5 V input span as specified in the AD9240 DC

SPECIFICATIONS.

Referring to Figure 24, the differential SHA is implemented

using a switched-capacitor topology. Hence, its input imped-

ance and its subsequent effects on the input drive source should

be understood to maximize the converter’s performance. The

combination of the pin capacitance, CPIN, parasitic capacitance

CPAR, and the sampling capacitance, CS, is typically less than

16 pF. When the SHA goes into track mode, the input source

must charge or discharge the voltage stored on CS to the new

input voltage. This action of charging and discharging CS which

is approximately 4 pF, averaged over a period of time and for a

given sampling frequency, FS, makes the input impedance ap-

pear to have a benign resistive component (i.e., 83 kΩ at FS =

10 MSPS). However, if this action is analyzed within a sam-

pling period (i.e., T = <1/FS), the input impedance is dynamic

due to the instantaneous requirement of charging and discharg-

ing CS. A series resistor inserted between the input drive source

and the SHA input as shown in Figure 28 provides effective

isolation.

VCC

AD9240

RS*

VINA

RS*

VINB

VEE

VREF

10F

0.1F

SENSE

REFCOM

*OPTIONAL SERIES RESISTOR

Figure 28. Series Resistor Isolates Switched-Capacitor

SHA Input from Op Amp. Matching Resistors Improve

SNR Performance

The optimum size of this resistor is dependent on several fac-

tors, which include the AD9240 sampling rate, the selected op

amp and the particular application. In most applications, a

30 Ω to 50 Ω resistor is sufficient; however, some applications

may require a larger resistor value to reduce the noise band-

width or possibly limit the fault current in an overvoltage

condition. Other applications may require a larger resistor value

as part of an antialiasing filter. In any case, since the THD

performance is dependent on the series resistance and the above

mentioned factors, optimizing this resistor value for a given

application is encouraged.

A slight improvement in SNR performance and dc offset

performance is achieved by matching the input resistance con-

nected to VINA and VINB. The degree of improvement is de-

pendent on the resistor value and the sampling rate. For series

resistor values greater than 100 Ω, the use of a matching resis-

tor is encouraged.

The noise or small-signal bandwidth of the AD9240 is the same

as its full-power bandwidth. For noise sensitive applications, the

excessive bandwidth may be detrimental and the addition of a

series resistor and/or shunt capacitor can help limit the wide-

band noise at the A/D’s input by forming a low-pass filter. Note,

however, that the combination of this series resistance with the

equivalent input capacitance of the AD9240 should be evalu-

ated for those time-domain applications that are sensitive to the

input signal’s absolute settling time. In applications where har-

monic distortion is not a primary concern, the series resistance

may be selected in combination with the SHA’s nominal 16 pF

of input capacitance to set the filter’s 3 dB cutoff frequency.

A better method of reducing the noise bandwidth, while possi-

bly establishing a real pole for an antialiasing filter, is to add

some additional shunt capacitance between the input (i.e.,

VINA and/or VINB) and analog ground. Since this additional

shunt capacitance combines with the equivalent input capaci-

tance of the AD9240, a lower series resistance can be selected to

establish the filter’s cutoff frequency while not degrading the

distortion performance of the device. The shunt capacitance

also acts as a charge reservoir, sinking or sourcing the additional

charge required by the hold capacitor, CH, further reducing

current transients seen at the op amp’s output.

The effect of this increased capacitive load on the op amp driv-

ing the AD9240 should be evaluated. To optimize performance

when noise is the primary consideration, increase the shunt

capacitance as much as the transient response of the input signal

will allow. Increasing the capacitance too much may adversely

affect the op amp’s settling time, frequency response and distor-

tion performance.

–10–

REV. B

11 Page | ||

| Páginas | Total 25 Páginas | |

| PDF Descargar | [ Datasheet AD9240.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| AD9240 | Monolithic A/D Converter | Analog Devices |

| AD9241 | Complete 14-Bit/ 1.25 MSPS Monolithic A/D Converter | Analog Devices |

| AD9243 | Monolithic A/D Converter | Analog Devices |

| AD9244 | 14-Bit 40/65 MSPS Monolithic A/D Converter | Analog Devices |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |