|

|

PDF WT6014 Data sheet ( Hoja de datos )

| Número de pieza | WT6014 | |

| Descripción | Digital Monitor Controller | |

| Fabricantes | ETC | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de WT6014 (archivo pdf) en la parte inferior de esta página. Total 19 Páginas | ||

|

No Preview Available !

WT6014

Digital Monitor Controller

Ver. 1.21 Jul-31-1998

GENERAL DESCRIPTION

The WT6014 is a member of WT60XX microcontroller family. It is specially designed for digital

controlled multi-sync monitor. It contains 8-bit CPU, 4K bytes ROM, 128 bytes RAM, 14 PWMs,

parallel I/O, SYNC processor, timer, DDC interface (slave mode I2C interface with DDC1), and

watch-dog timer.

FEATURES

* 8-bit 6502 compatible CPU, 4MHz operating frequency

* 4096 bytes ROM, 128 bytes SRAM

* 8MHz crystal oscillator

* 14 channels 8-bit/62.5kHz PWM outputs (8 open drain outputs & 6 CMOS outputs)

* Sync signal processor with sync separation, frequency calculation, H/V polarity detection control

* DDC interface supports VESA DDC1/DDC2B standard

* Watch-dog timer (0.524 second)

* Maximum 22 programmable I/O pins

* One 8-bit programmable timer

* One external interrupt request

* Built-in low VDD voltage reset

* Single +5V power supply

PIN ASSIGNMENT

40-Pin PDIP

DA2

DA1

DA0

RESET

VDD

GND

OSCO

OSCI

PB5

PB4

PB3

PB2

PB1

PB0

IRQ

PC7

PC6

PC5

PC4

PC3

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

40 VSYNC

39 HSYNC

38 DA3

37 DA4

36 DA5

35 DA6

34 DA7

33 PA7/HSO

32 PA6/VSO

31 PA5/DA13

30 PA4/DA12

29 PA3/DA11

28 PA2/DA10

27 PA1/DA9

26 PA0/DA8

25 SCL

24 SDA

23 PC0

22 PC1

21 PC2

42-Pin SDIP

DA2

DA1

DA0

RESET

VDD

GND

OSCO

OSCI

PB5

PB4

PB3

PB2

PB1

PB0

IRQ

PC7

PC6

PC5

PC4

PC3

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

42 VSYNC

41 HSYNC

40 DA3

39 DA4

38 DA5

37

36 DA6

35 DA7

34 PA7/HSO

33 PA6/VSO

32 PA5/DA13

31 PA4/DA12

30 PA3/DA11

29 PA2/DA10

28 PA1/DA9

27 PA0/DA8

26 SCL

25 SDA

24 PC0

23 PC1

22 PC2

* I2C is a trademark of Philips Corporation.

* DDC is a trademark of Video Electronics Standard Association (VESA).

Weltrend Semiconductor, Inc.

1

1 page

I/O Ports

WT6014

Digital Monitor Controller

Ver. 1.21 Jul-31-1998

Port_A :

Pin PA0/DA8

Pin PA1/DA9

Pin PA2/DA10

Pin PA3/DA11

Pin PA4/DA12

Pin PA5/DA13

Pin PA6/VSO

Pin PA7/HSO

- general purpose I/O shared with DA8 output.

- general purpose I/O shared with DA9 output.

- general purpose I/O shared with DA10 output.

- general purpose I/O shared with DA11 output.

- general purpose I/O shared with DA12 output.

- general purpose I/O shared with DA13 output.

- general purpose I/O shared with VSYNC output.

- general purpose I/O shared with HSYNC output.

Port_A is controlled by REG#10H & REG#11H. In REG#10H, each corresponding bit enables

HSYNC output, VSYNC output or D/A converter output when it is "1". If the corresponding bit is "0",

the output level is decided by REG#11H. In REG#11H, if the I/O corresponding bit (PAn) is "0", the

output is low level (IOL=5mA). If PAn bit is "1", the output is high level (IOH= -100uA) and can be

used as an input.

Address

0010H

0011H

0011H

R/W

W

W

R

Initial

00H

FFH

--

Bit7

EHO

PA7W

PA7R

Bit6

EVO

PA6W

PA6R

Bit5

EDA13

PA5W

PA5R

Bit4

EDA12

PA4W

PA4R

Bit3

EDA11

PA3W

PA3R

Bit2

EDA10

PA2W

PA2R

Bit1

EDA9

PA1W

PA1R

Bit0

EDA8

PA0W

PA0R

Bit Name

EHO

EVO

EDA13

EDA12

EDA11

EDA10

EDA9

EDA8

PA7W - PA0W

PA7R- PA0R

Bit value = “1”

Enable PA7 as HSYNC output.

Enable PA6 as VSYNC output.

Enable PA5 as DA13 output.

Enable PA4 as DA12 output.

Enable PA3 as DA11 output.

Enable PA2 as DA10 output.

Enable PA1 as DA9 output.

Enable PA0 as DA8 output.

Outputs high level (IOH= -100uA).

Pin is high level.

Bit value = “0”

PA7 as general purpose I/O.

PA6 as general purpose I/O.

PA5 as general purpose I/O.

PA4 as general purpose I/O.

PA3 as general purpose I/O.

PA2 as general purpose I/O.

PA1 as general purpose I/O.

PA0 as general purpose I/O.

Outputs low level (IOL= 5mA).

Pin is low level.

* If the program wants to force VSYNC output (VSO pin) in low state, write "0" to PA6 bit first, then

write "0" to EVO bit. This is used to prevent high frequency output on VSO pin when the VSYNC

frequency is increased to read EDID data in DDC1 mode.

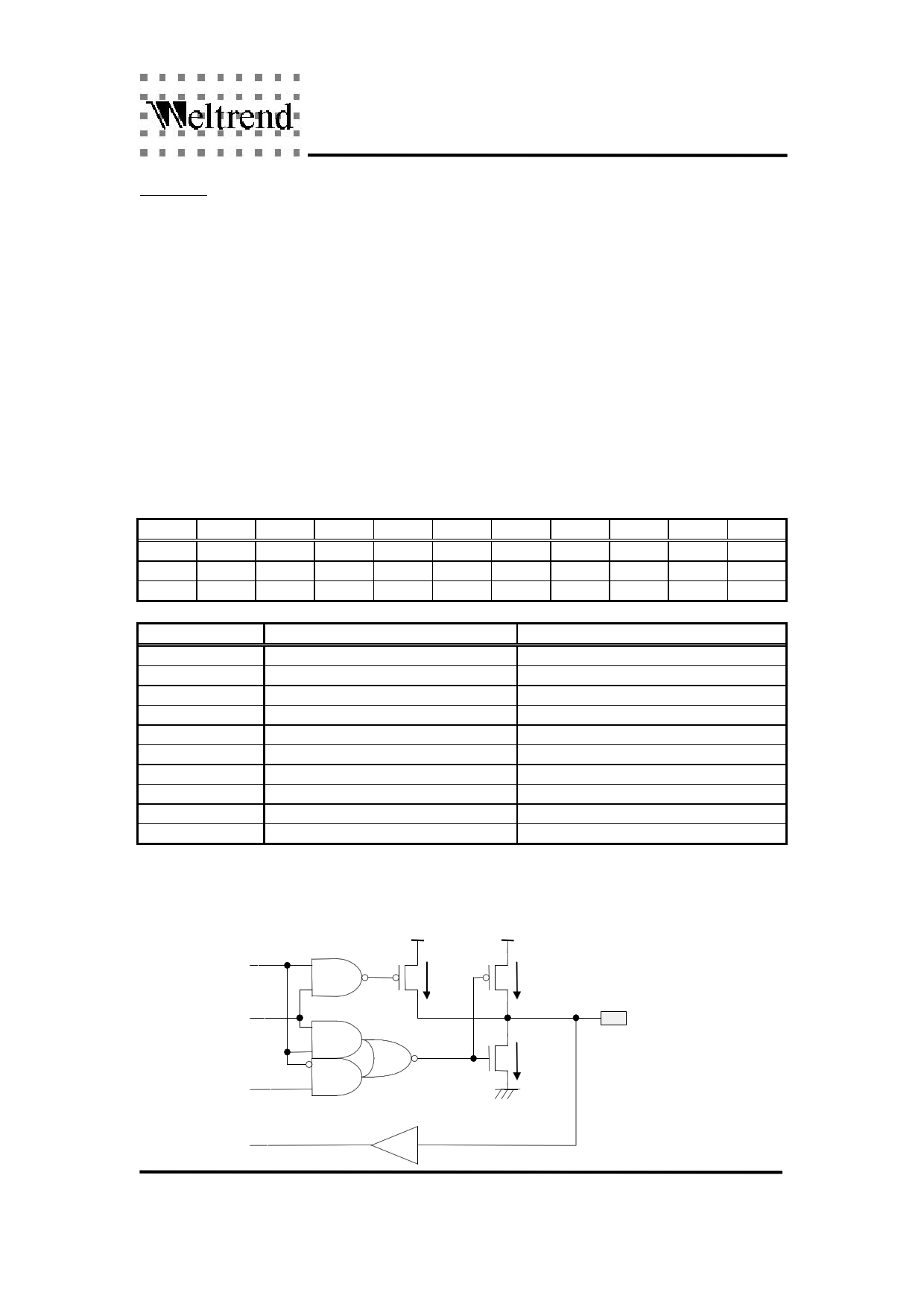

EDAx

DAx

PAnW

5mA

100uA

5mA

Pin PAn

PAnR

Weltrend Semiconductor, Inc.

5

5 Page

WT6014

Digital Monitor Controller

Ver. 1.21 Jul-31-1998

(5) Data bytes transmit/receive

If the RW bit is "1", the shift register will load data from the data buffer (REG#18H) before the

data

byte is transmitted and shift out data to the SDA pin before the rising edge of the SCL clock.

If the RW bit is "0", the shift register will shift in data on the rising edge of the SCL clock and the

whole data byte is latched to the data buffer(REG#18H).

(6) Handshaking procedure

The handshaking is done on the byte level. The DDC interface will hold the SCL pin low after the

acknowledge bit automatically. The bus master will be forced to wait until the WT6014 is ready for

the next byte transfer. To release the SCL pin, write REG#19H will release clear the wait state.

(7) Interrupt INT0

The DDC interface interrupt is enabled by setting the IEN_D bit in the REG#1AH.

Interrupt INT0 occurs when:

- Transmit buffer empty in DDC1 state.

The INT0 occurs when the shift register load data from data buffer.

Write REG#18H will clear the transmit buffer empty condition.

- Acknowledge is detected in DDC2B state.

The INT0 occurs on the falling edge of the SCL clock after the acknowledge had been

detected.

The SCL pin will be pulled low to force the bus master to wait until the REG#19H is written.

- STOP condition occurs in DDC2B state

Address

0018H

0019H

0019H

R/W

R/W

R

W

Initial

FFH

40H

A0H

Bit7 Bit6

D7 D6

DDC2B ADDR

A6 A5

Bit5 Bit4 Bit3

D5 D4 D3

RW START STOP

A4 A3 A2

Bit2

D2

--

A1

Bit1 Bit0

D1 D0

-- --

A0 ENACK

Bit Name

DDC2B

ADDR

RW

START

STOP

ENACK

A6,A5, …., A0

D7,D6, …., D0

Bit value = “1”

Bit value = “0”

DDC2B state.

DDC1 state.

received address equals to the address received address equals to ‘1010000’.

in REG#19H(W).

received R/W bit is ‘1’.

received R/W bit is ‘0’.

START condition is detected.

No START condition is detected.

STOP condition is detected.

No STOP condition is detected.

Enable acknowledge.

Disable acknowledge.

7-bit slave address

Data to be transmitted or received data.

Weltrend Semiconductor, Inc.

11

11 Page | ||

| Páginas | Total 19 Páginas | |

| PDF Descargar | [ Datasheet WT6014.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| WT6014 | Digital Monitor Controller | ETC |

| WT6016 | Digital Monitor Controller | ETC |

| WT6018 | Digital Monitor Controller | ETC |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |