|

|

PDF ICS83115BRT Data sheet ( Hoja de datos )

| Número de pieza | ICS83115BRT | |

| Descripción | LOW SKEW/ 1-TO-16 LVCMOS / LVTTL FANOUT BUFFER | |

| Fabricantes | Integrated Circuit Systems | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ICS83115BRT (archivo pdf) en la parte inferior de esta página. Total 9 Páginas | ||

|

No Preview Available !

Integrated

Circuit

Systems, Inc.

ICS83115

LOW SKEW, 1-TO-16

LVCMOS / LVTTL FANOUT BUFFER

GENERAL DESCRIPTION

ICS

The ICS83115 is a low skew, 1-to-16 LVCMOS/

LVTTL Fanout Buffer and a member of the

HiPerClockS™ HiPerClockS™ family of High Performance Clock

Solutions from ICS. The ICS83115 single ended

clock input accepts LVCMOS or LVTTL input lev-

els. The ICS83115 operates at full 3.3V supply mode over the

commercial temperature range. Guaranteed output and part-to-

part skew characteristics make the ICS83115 ideal for those

clock distribution applications demanding well defined perfor-

mance and repeatability.

FEATURES

• 16 LVCMOS/LVTTL outputs

• 1 LVCMOS/LVTTL clock input

• Maximum output frequency: 200MHz

• All inputs are 5V tolerant

• Output skew: 250ps (maximum)

• Part-to-part skew: 800ps (maximum)

• Additive phase jitter, RMS: 0.09ps (typical)

• 3.3V operating supply

• 0°C to 70°C ambient operating temperature

• Lead-Free package available

• Industrial temperature information available upon request

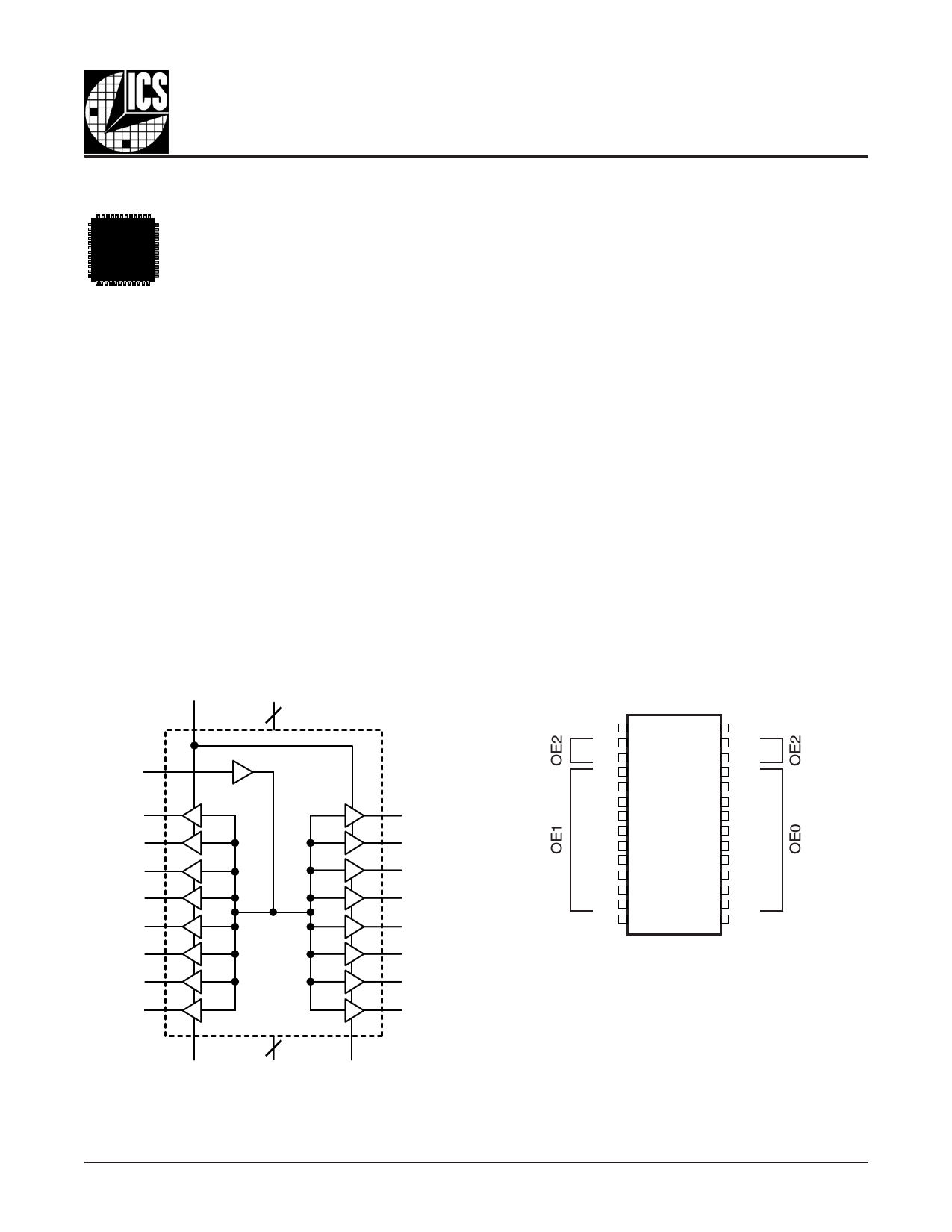

BLOCK DIAGRAM

OE2

VDD

4

IN

Q0

Q1

Q2

Q3

Q4

Q5

Q6

Q7

OE1

4

GND

Q15

Q14

Q13

Q12

Q11

Q10

Q9

Q8

OE0

PIN ASSIGNMENT

OE1

Q0

Q1

Q2

VDD

VDD

Q3

Q4

GND

GND

Q5

Q6

Q7

IN

1

2

3

4

5

6

7

8

9

10

11

12

13

14

28 OE2

27 Q15

26 Q14

25 Q13

24 VDD

23 VDD

22 Q12

21 Q11

20 GND

19 GND

18 Q10

17 Q9

16 Q8

15 OE0

ICS83115

28-Lead SSOP, 150mil

9.9mm x 3.9mm x 1.7mm body package

R Package

(Top View)

83115BR

www.icst.com/products/hiperclocks.html

1

REV. A SEPTEMBER 21, 2004

1 page

Integrated

Circuit

Systems, Inc.

ICS83115

LOW SKEW, 1-TO-16

LVCMOS / LVTTL FANOUT BUFFER

ADDITIVE PHASE JITTER

The spectral purity in a band at a specific offset from the funda-

mental compared to the power of the fundamental is called the

dBc Phase Noise. This value is normally expressed using a

Phase noise plot and is most often the specified plot in many

applications. Phase noise is defined as the ratio of the noise

power present in a 1Hz band at a specified offset from the fun-

damental frequency to the power value of the fundamental. This

ratio is expressed in decibels (dBm) or a ratio of the power in

the 1Hz band to the power in the fundamental. When the re-

quired offset is specified, the phase noise is called a dBc value,

which simply means dBm at a specified offset from the funda-

mental. By investigating jitter in the frequency domain, we get a

better understanding of its effects on the desired application over

the entire time record of the signal. It is mathematically possible

to calculate an expected bit error rate given a phase noise plot.

0

-10

-20

-30

-40

-50

-60

-70

-80

-90

-100

-110

-120

-130

-140

-150

-160

-170

-180

-190

1k

Additive Phase Jitter, RMS

@ 155.52MHz (12KHz to 20MHz)

= 0.09ps typical

10k 100k 1M 10M

OFFSET FROM CARRIER FREQUENCY (HZ)

100M

As with most timing specifications, phase noise measurements

have issues. The primary issue relates to the limitations of the

equipment. Often the noise floor of the equipment is higher than

the noise floor of the device. This is illustrated above. The de-

vice meets the noise floor of what is shown, but can actually be

lower. The phase noise is dependant on the input source and

measurement equipment.

83115BR

www.icst.com/products/hiperclocks.html

5

REV. A SEPTEMBER 21, 2004

5 Page | ||

| Páginas | Total 9 Páginas | |

| PDF Descargar | [ Datasheet ICS83115BRT.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ICS83115BRLFT | LOW SKEW/ 1-TO-16 LVCMOS / LVTTL FANOUT BUFFER | Integrated Circuit Systems |

| ICS83115BRT | LOW SKEW/ 1-TO-16 LVCMOS / LVTTL FANOUT BUFFER | Integrated Circuit Systems |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |